#### RICERCA DI SISTEMA ELETTRICO

Attività analitiche a supporto del progetto di canali sperimentali per Jules Horowitz Reactor (JHR )

Mauro Cappelli

ATTIVITÀ ANALITICHE A SUPPORTO DEL PROGETTO DI CANALI SPERIMENTALI PER JULES HOROWITZ REACTOR (JHR ) *Mauro Cappelli ENEA* Settembre 2012

Report Ricerca di Sistema Elettrico

Accordo di Programma Ministero dello Sviluppo Economico - ENEA Area: Governo, Gestione e Sviluppo, del Sistema Elettrico Nazionale

Progetto: Nuovo Nucleare da Fissione: Collaborazioni Internazionali e sviluppo Competenze in Materia

Nucleare

Responsabile del Progetto: Massimo Sepielli, ENEA

|                                | Sigla di identificazione | Distrib. | Pag. | di |

|--------------------------------|--------------------------|----------|------|----|

| ENEA Ricerca Sistema Elettrico | PAR2011-ENEA-L1B2-021    | L        | 1    | 8  |

#### **Titolo**

Attività analitiche a supporto del progetto di canali sperimentali per Jules Horowitz Reactor (JHR)

#### Descrittori

Tipologia del documento:

Rapporto Tecnico

Collocazione contrattuale: ACCORDO DI PROGRAMMA Ministero dello Sviluppo Economico – ENEA sulla Ricerca di Sistema Elettrico PIANO ANNUALE DI REALIZZAZIONE 2011

Progetto 1.3.1: Energia nucleare: NUOVO NUCLEARE DA FISSIONE: COLLABORAZIONI INTERNAZIONALI E SVILUPPO COMPETENZE IN MATERIA NUCLEARE, PAR 2011.

**Argomenti trattati:** Termoidraulica, Meccanica strutturale, Normativa tecnica, Sistemi di controllo, Fisica dei Reattori Nucleari, Neutronica, Schermaggio delle Radiazioni, Metodo Montecarlo

#### Sommario

Il presente documento descrive l'attività svolta in collaborazione tra ENEA e CEA su temi legati allo sviluppo del nuovo reattore sperimentale Jules Horowitz Reactor (JHR) in costruzione a Cadarache (Francia) da un consorzio internazionale (comprendente anche l'Unione Europea) sotto l'egida dell'OECD/NEA.

L'ENEA partecipa secondo varie forme di collaborazione sia direttamente con i propri ricercatori sia attraverso collaborazione bilaterale con le singole Università italiane.

In questo documento è riportato il risultato della collaborazione già iniziata nelle annualità precedenti tra ENEA, CIRTEN (nella fattispecie, l'Università di Bologna) e JHR per la progettazione di canali sperimentali del costruendo reattore. In particolare, il documento riporta uno studio sull'apporto di potenza generata da sezioni di prova contenenti elementi "attivi" nel caso di spegnimento del reattore in condizioni normali e in condizioni di sicurezza (safety shutdown).

Parallelamente a questa attività, si è iniziata una nuova linea di collaborazione sulla strumentazione e il controllo volta al progetto di nuovi sistemi avanzati da impiegare nelle facilities sperimentali in corso di completamento. L'attività svolta, descritta nei due deliverables allegati, redatti a cura dell'Università dell'Aquila, rappresenta uno studio preliminare per sistemi di controllo avanzati da applicare in reattori di nuova concezione.

#### Note

Copia n.

#### In carico a:

| 2    |             |           | NOME  |             |                   |              |

|------|-------------|-----------|-------|-------------|-------------------|--------------|

|      |             |           | FIRMA |             |                   |              |

| 1    |             |           | NOME  |             |                   |              |

| _    |             |           | FIRMA |             |                   |              |

| 0    | EMISSIONE   | 25/9/2012 | NOME  | M. Cappelli | P.C. Incalcaterra | M. Sepielli  |

|      | EMISSIONE   | 23/3/2012 | FIRMA | Mes         | Tieneslety        | it Ill.      |

| REV. | DESCRIZIONE | DATA      |       | REDAZIONE   | CONVALIDA         | APPROVAZIONE |

#### **Sommario**

| Descrizione Generale Della Partecipazione Enea Al Progetto Jules Horowitz          | _ |

|------------------------------------------------------------------------------------|---|

| Reactor (JHR)                                                                      | 3 |

| ALL. 1: Power Transient Analyses For Reflector Experimental Devices During         |   |

| Shutdowns In Jules Horowitz Reactor                                                | 6 |

| ALL. 2: Study And Analysis Of Control Systems Implementable By Programmable        |   |

| Logic For Performance And Safety Improvements Of Novel Nuclear Plants              | 7 |

| ALL. 3: Development of a Simulation Environment for the Analysis of Control        |   |

| <b>System Performance for Performance and Safety Improvements of Novel Nuclear</b> |   |

| Plants                                                                             | 8 |

|                           | Sigla di identificazione |   | Distrib. | Pag. | di |

|---------------------------|--------------------------|---|----------|------|----|

| Ricerca Sistema Elettrico | PAR2011-ENEA- L1P1 -021  | 0 | L        | 3    | 8  |

## Descrizione Generale Della Partecipazione Enea Al Progetto Jules Horowitz Reactor (JHR)

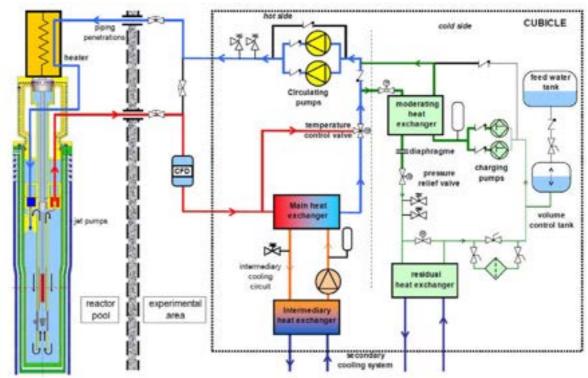

Il PAR 2011 prevede il prosieguo della collaborazione con CEA nella fase di progettazione del reattore Jules Horowitz per sperimentazioni su materiali e sistemi per retattori nucleari di attuale e futura generazione. ENEA e CIRTEN (Università di Bologna) hanno sviluppato uno studio che si colloca nella partecipazione alla progettazione di canali sperimentali del reattore "Jules Horowitz Reactor (JHR)", al momento in corso di costruzione presso il Centro CEA di Cadarache. In questo ambito, l'attività ENEA-CIRTEN ha riguardato le simulazioni neutroniche e termoidrauliche a supporto della progettazione di alcuni canali sperimentali dello JHR. Nuove attività potranno riguardare la progettazione di prove sperimentali appropriate per la validazione di codici di calcolo per la sicurezza nucleare.

La ricerca europea si avvale di numerosi reattori realizzati specificatamente per studi sui materiali (Material Testing Reactors, MTR), finalizzati all'avanzamento tecnologico del progetto degli impianti nucleari di potenza. Il reattore Jules Horowitz (JHR) è un rettore di ricerca da 100 MWth del tutto innovativo nello scenario dei reattori sia europei che mondiali: infatti è stato progettato per produrre contemporaneamente un flusso di neutroni veloci nel core del reattore ed un flusso di neutroni termici nella zona circostante il core, realizzata con un mantello di berillio, adeguatamente configurato sia per espletare la funzione di riflettore sia per ospitare apposite sezioni di prova (si veda l'allegato Power Transient Analyses For Reflector Experimental Devices During Shutdowns In Jules Horowitz Reactor per una descrizione più accurata del reattore e per informazioni più dettagliate sulle sue caratteristiche).

Ambedue i flussi neutronici raggiungono valori molto elevati  $(2 \div 4 \times 10^{14} \text{ n/cmq*s per il flusso veloce} = 5 \times 10^{13} \div 5 \times 10^{14} \text{ n/cmq*s per il flusso termico})$ : questa caratteristica, unita ad un accurato progetto della zona reattore – mantello, fa sì che nel core e nel moderatore di JHR possano essere alloggiate sezioni di prova che sono anche configurabili come veri loop sperimentali. Esse consentono di simulare, in condizioni termoidrauliche e nucleari reali, situazioni operative di particolare criticità per reattori di IV generazione, con riferimento soprattutto a quelli di interesse per il Sustainable Nuclear Energy Technology Platform in ambito UE (reattori veloci a Sodio, a piombo o piombo-bismuto, a gas). In particolare gli alti flussi neutronici conseguibili consentono di produrre elevati "dpa rate" (8 $\div$ 16 dpa/year), permettendo di sperimentare, in tempi ragionevolmente brevi, gli effetti degli irraggiamenti su quei materiali che si prevede potranno essere impiegati in reattori di IV generazione .

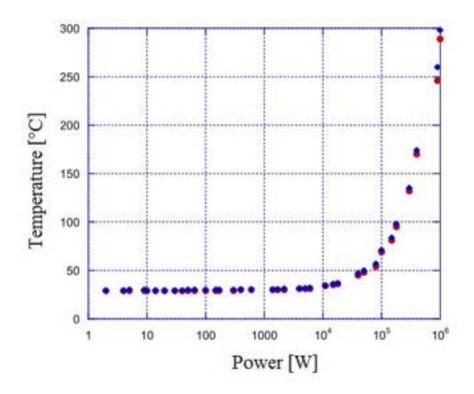

JHR può ospitare numerose sezioni di prova contenenti anche elementi di combustibile, da provare all'interno del reattore stesso: gli alti flussi tipici di JHR chiaramente inducono, nei combustibili presenti nelle sezioni di prova che li ospitano, potenze termiche lineari consistenti, dipendenti dall'arricchimento del combustibile in prova, ma comunque sempre dell'ordine di parecchie centinaia di W/cm. Infatti un combustibile sperimentale con arricchimento già dell'1% in U 235,quando sottoposto

al flusso di neutroni termici presente nel mantello, può raggiungere una potenza termica lineare di 600 W/cm.

JHR consentirà in definitiva, la raccolta di moltissimi dati sperimentali di importanza essenziale sia per approfondire aspetti riguardante l'esistente famiglia di reattori già operativi sia per avere evidenze sperimentali sulle interazioni dei neutroni con materiali/leghe innovativi, sul comportamento dei combustibili nelle varie combinazioni attualmente in studio (build-up dei gas di fissione, bruciamento degli attinidi ed altro) su processi di trasmutazione etc.

Il presente lavoro, descritto nell'allegato Power Transient Analyses For Reflector Experimental Devices During Shutdowns In Jules Horowitz Reactor, si propone di studiare l'apporto di potenza generata da sezioni di prova contenenti elementi "attivi" installati nel reattore per scopi di ricerca, nel caso di spegnimento del reattore in condizioni normali e in condizioni di sicurezza (safety shutdown). Si è supposta pertanto la contemporanea presenza di più sezioni di prova contenenti elementi di combustibile ovvero costituite esclusivamente da specifici elementi di combustibile (è questo il caso di sperimentazioni previste in appositi canali del core e del riflettore.), il cui apporto di potenza dovrà essere tenuto in conto in caso di spegnimento per il dimensionamento del sistema di raffreddamento.

Proprio per la presenza di tali sezioni di prova "attive" che danno un contributo di potenza anche dopo lo spegnimento del reattore è importante definire l'evoluzione della temperatura in caso di shut-down per manovre di normale esercizio o di safety.

Lo studio fa riferimento a progetti di sezioni di prova già definiti ovvero in avanzato stato di definizione, e che quindi potranno verosimilmente essere installate contemporaneamente su JHR.

Le analisi sono state condotte con codice DULCINEE (cinetica neutronica) e TRIPOLI 4.7 Monte Carlo (accoppiamento core-riflettore), ed assumendo alcune ipotesi significative circa la sequenza di inserzione delle barre di controllo.

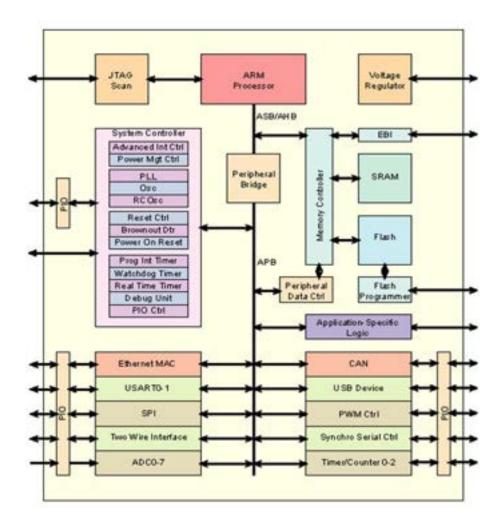

Una nuova linea di ricerca è stata introdotta in tale collaborazione a partire dalla presente annualità. Una delle ultime fasi del progetto di un reattore nucleare (per la produzione elettrica o a scopo di ricerca) è tipicamente dedicata all'implementazione della strumentazione e dei sistemi di acquisizione dati, controllo e protezione a garanzia della sicurezza.

L'ENEA ha iniziato su questi temi una collaborazione con il JHR, anche attraverso il contributo dell'Università dell'Aquila e del DEWS (Centro di Eccelenza dello stesso Ateneo).

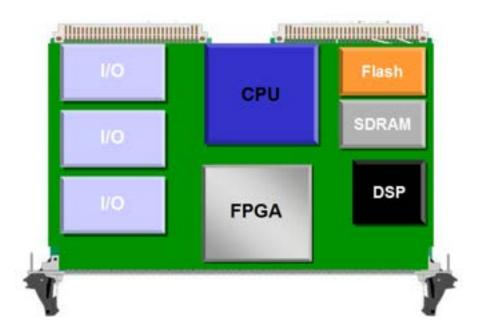

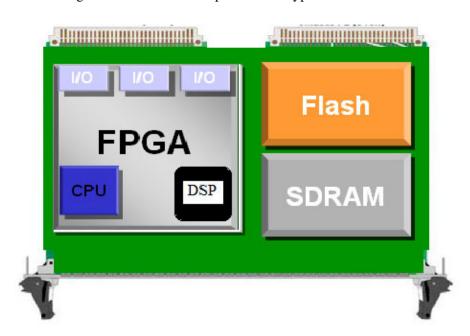

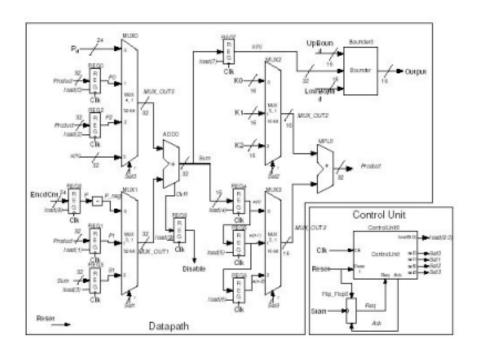

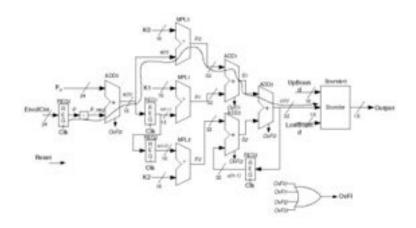

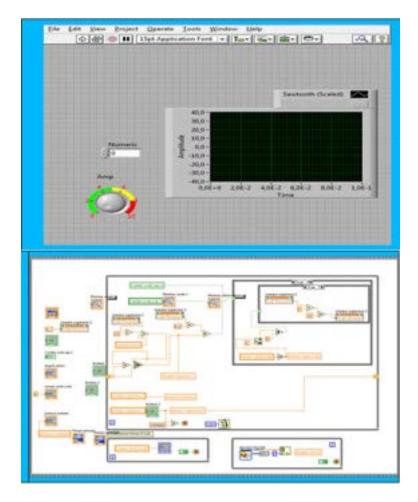

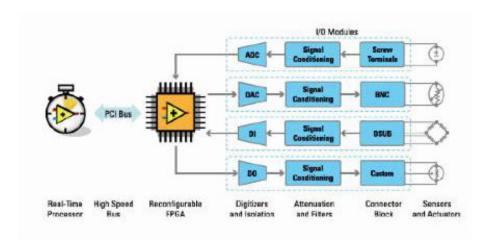

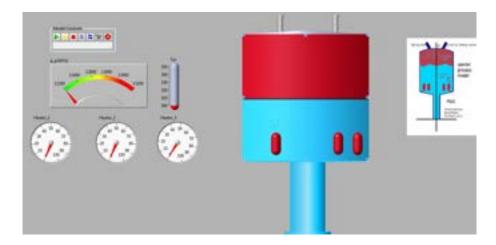

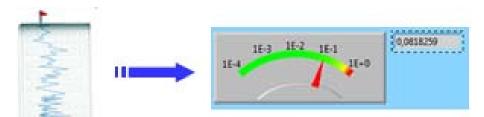

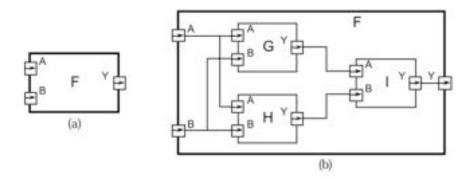

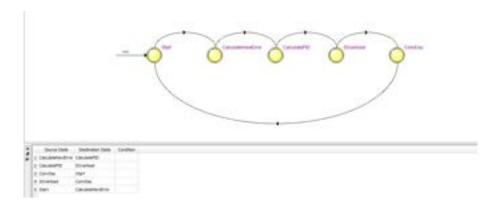

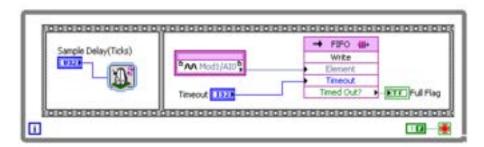

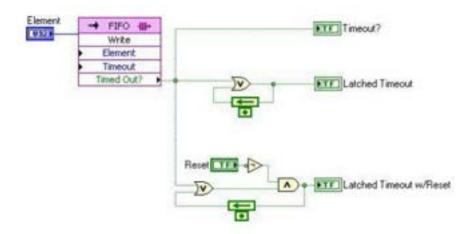

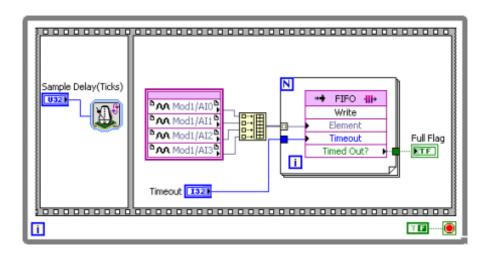

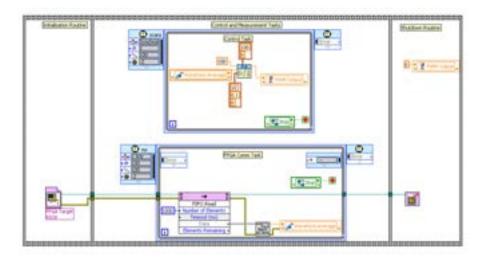

In questa annualità, è stato svolto uno studio preliminare volto all'indagine delle potenzialità di alcuni dispositivi innovativi come gli FPGA (Field Programmabale Gate Array) sui sistemi di comando e controllo dei reattori nucleari di generazione avanzata e sulle principali criticità che si riscontrano nella realizzazione di prodotti hardware e software volti alla mitigazione o risoluzione delle problematiche legati alla sicurezza d'impianto e all'ottimizzazione delle performances rispetto a quanto previsto da progetto.

L'attività ha interessato lo studio e l'analisi dello stato dell'arte dei sistemi di controllo oggi implementati e in via di sviluppo, con particolare attenzione a implementazioni che coinvolgano logiche programmabili. Una volta acquisiti i riferimenti scientifici, si è provveduto a uno studio di fattibilità sulla realizzazione di un sistema di controllo basato su tecnologia FPGA e quindi alla progettazione di un prototipo di tipo *general purpose*.

Tale studio risulta di particolare importanza come valutazione preliminare alla progettazione di un sistema di controllo remoto di tipo DCS (Distributed Control System), in corso di definizione all'interno della collaborazione con il JHR. Tipicamente, il progetto si basa su componentistica "classica" di tipo PLC, con sistema di supervisione centralizzato.

Tali PLC sono distribuiti in zone dedicate alle esperienze (p.e. nella zona dei canali sperimentali) e controllate da una sala controllo che ha il compito di gestirne l'affidabilità in ogni istante.

Tale sistema, che è integrato in una rete di interconnessione ridondata ad alta affidabilità e alto flusso di dati, con server per lo smistamento dei dati e stazioni di supervisione e verifica di correttezza dei dati, potrebbe essere implentato anche in una tecnologia più innovativa come gli FPGA, le cui potenzialità sono in fase di valutazione a livello internazionale per tutte le tipologie di impianto.

L'industria nucleare sta infatti indagando sempre più, negli ultimi tempi, il ricorso a tecnologie più innovative e in grado di garantire una migliore personalizzazione per applicazioni del mondo nucleare. Tra queste nuove tecnologie, si segnalano per qualità e prestazioni gli ASIC (Application Specific Integrated Circuit), i CPLD (Complex Programmable Logic Device) e gli FPGA (Field Programmable Gate Array).

Tali dispositivi condividono la comune caratteristica di programmabilità da parte dell'utente, che consente di personalizzare sia l'hardware che il software alla specifica applicazione richiesta, senza dover passare per hardware e software generali (e spesso sovradimensionati rispetto alle reali necessità), garantendo così tra le altre cose una maggiore immunità alle intrusioni indesiderate contro la riservatezza dei dati.

In tale contesto, rivestono sempre più successo le architetture FPGA, che garantiscono linguaggi di programmazione altamente sviluppati come Verilog o VHDL, capaci di tradurre più agelvolmente funzioni complesse nella tecnologia richiesta.

Con l'intento di indagare le potenzialità di tale tecnologia è stato acquisito un sistema commerciale basato su tecnologia FPGA programmabile tramite linguaggio ad alto livello LabVIEW© (confronta rapporto PAR2011-ENEA-L1B2-014).

|                           | Sigla di identificazione |   |   | Pag. | di |

|---------------------------|--------------------------|---|---|------|----|

| Ricerca Sistema Elettrico | PAR2011-ENEA- L1P1 -021  | 0 | L | 6    | 8  |

## ALL. 1: Power Transient Analyses For Reflector Experimental Devices During Shutdowns In Jules Horowitz Reactor

#### **CIRTEN**

#### <u>C</u>onsorzio <u>I</u>nteruniversitario per la <u>R</u>icerca <u>TE</u>cnologica <u>N</u>ucleare

#### UNIVERSITA' DI BOLOGNA

## Dipartimento di Ingegneria Energetica, Nucleare e del Controllo Ambientale DIENCA

## Progettazione neutronica e termofluidodinamica di canali sperimentali di reattori di ricerca

# POWER TRANSIENT ANALYSES FOR REFLECTOR EXPERIMENTAL DEVICES DURING SHUTDOWNS IN JULES HOROWITZ REACTOR (JHR)

Autori

UNIBO: Patrizio Console Camprini

Carlo Artioli Marco Sumini Francesco Teodori

CEA: Christian Gonnier

Bernard Pouchin Serge Bourdon

**CERSE-UNIBO RL 1353/2012**

**BOLOGNA, 31 LUGLIO 2012**

#### **Abstract**

European nuclear research takes advantage of several Material Testing Reactors (MTRs) aiming at technological enhancement of power plants design and operation to support industries, utilities and regulators. Jules Horowitz Reactor (JHR) is intended to be the 100 MW MTR that attains the most significant experimental capacity in Europe. It is designed to host several devices and fuel experiments are planned to be performed inside the reflector. Since some fuel samples will be loaded within this area, a power transient evaluation is important to define temperature evolution during shutdowns for safety and reactor operation purposes. The present analysis considers Normal and Safety Shutdown procedures and takes into account different compositions concerning the equilibrium cycle.

### Index

| Index                                                              |    |

|--------------------------------------------------------------------|----|

| 1 Introduction                                                     |    |

| 1 III(I OddCtiOII                                                  |    |

| 1 The Jules Horowitz Reactor Project                               | 4  |

| 1.1 European Material Testing Reactor for Research and Development | 4  |

| 1.2 Reactor Core Description                                       | 5  |

| 1.3 JHR Experimental Capacity                                      | 6  |

| 2 Research Description                                             | 19 |

| 2.1 Thermalhydraulic and Neutronic Core Model                      | 19 |

| 2.2 Shutdown Systems for JHR                                       | 20 |

| 2.3 Core-Reflector Coupling                                        | 21 |

| 2.4 Reflector Device Calculations                                  | 23 |

| 2.5 Conclusions and Perspectives                                   |    |

| 3 References                                                       | 27 |

#### 1 Introduction

#### 1 The Jules Horowitz Reactor Project

#### 1.1 European Material Testing Reactor for Research and Development

European policy regarding energy supply and resources availability, as well as infrastructures, is expected to gather different domestic power plant fleets searching more and more for shared scenarios. Growing demand for electrical power and greenhouse gases reduction strategies make nuclear energy a significant source in the European mix, since very low environmental impact and economical competitiveness are achieved.

At present time, several nuclear power plants are connected to the grid supplying around 30% of European electrical needs. Research and development supporting this significant network take advantage of Material Testing Reactors (MTR) which provide experimental data to industries, utilities and regulators. In fact, these facilities are very important to study properties of materials that have to withstand critical thermalhydraulic and radiation conditions during operation.

The French Atomic Energy Commission (CEA) has then launched the construction of a new MTR – the Jules Horowitz Reactor (JHR) - at Cadarache research centre in the framework of an international collaboration.

JHR is intended to become the most important MTR in Europe for the next century. It has been conceived in order to investigate structural material and fuel properties linking industrial and research needs of all partners.

- Sustainability of power supply is also related to energy market and then life extension of power plants is a key point in network management, aiming at reducing capital costs and enhancing competitiveness. GenII nuclear plant lifespan needs several material tests in order to keep the best safety level respecting components qualification procedure. So JHR is equipped with experimental loops able to simulate present PWR, BWR, CANDU and VVER technologies using both a core fast flux and a proper in-reflector thermal neutron spectrum. GenIII reactors deployment phase requires experimental R&D to support and validate material certification during all the long life of this innovative nuclear plant generation. On the other hand JHR allows fuel performances optimization through sample irradiation achieving higher burnup and better resource exploitation.

- Safety topics are investigated by means of accident simulations and component tests. LOCA (loss of coolant accident) scenarios are then reproduced, as well as power transients and ramps, in order to study fuel materials behaviour. In addition, data concerning fuel properties during normal and abnormal operations are provided for utilities and industries.

- High neutron fluxes and elevated temperature loops have been designed in order to reproduce challenging conditions for GenIV reactors research and development. A quite in-core fast neutron spectrum is also capable to reproduce SFR, GFR or LFR neutronic features. Preparing for next innovative GenIV reactors, many experimental data are needed concerning radiation interaction with advanced materials namely graphite, nickel alloys and ceramics. JHR has been conceived for sample selection and testing in representative conditions about neutron flux and thermal stresses. Ageing effects and mechanical deformation are expected to be reproduced as far as operational irradiation periods are concerned. High in-core DPA (Displacements Per Atom) rates allow important experiments aimed at improvement of cladding and in-vessel component materials such as austenitic stainless steel or ferritic steel (mainly utilized in sodium and lead-cooled technologies). In addition, optimized devices have been prepared to study minor actinides partitioning and transmutation issues. Fission gases build-up investigation is particularly focused on americium burning system analysis.

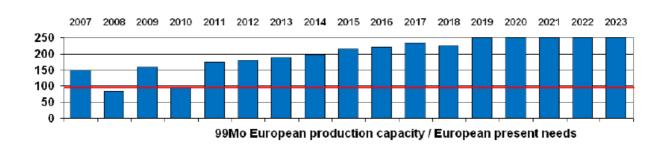

- Increasing in nuclear medicine diffusion and reliability makes radioisotope production and stock very important and strategic activities in the research reactor domain. JHR is going to be capable to supply from around 25% of European needs in Molybdenum-99 to about 50% in case of particular market demand or critical procurement.

Nuclear research always needs facilities for education and training of young scientists and engineers.

Then JHR international project is also aimed at expertise transfer and enhancement to support future European technology.

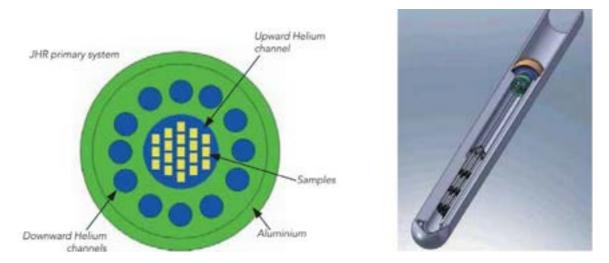

#### 1.2 Reactor Core Description

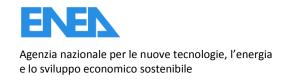

JHR is a 100 MW pool-type light water cooled material testing reactor which has been designed to achieve high experimental capacity. The core rack is a 60 cm height cylinder made of aluminium in which 37 drilled holes can host both 34 fuel elements and 3 sample holders within the so called "large" test positions. On the other hand, "small" test locations are placed in the centre of 7 cylindrical plate fuel elements in order to reach the fast flux as close as possible to the fuel. These 10 experimental slots are available at the same time in order to maximize fast neutron utilization for structural irradiation and high dpa rates.

Two different nominal conditions are envisaged to optimize experimental availability and operative costs: the first one is about 100 MW thermal power as described before and the second foresees some 70 MW. Even a possible twofold core charging is accepted: 37 or 34 fuel elements depending on test needs from international partners.

The operational cycle is about 25 days and a particular  $U_3Si_2$  metallic fuel 27% enriched in U235 is used. The ultimate fuel is expected to be a metallic UMo 19.75% enriched alloy which is still under qualification at present time, nevertheless it is planned to be supplied after the starting phase. The cladding material is an aluminium alloy and every fuel element is composed by 8 cylindrical and concentric plates kept together by 3 stiffeners.

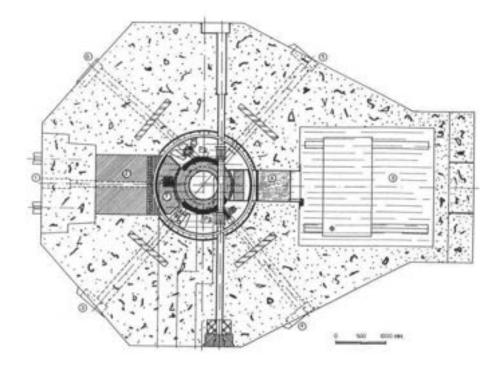

Figure 1) JHR core cross-section

Figure 2) JHR fuel element

Remaining 27 fuel elements not hosting sample holders are utilized for control rods insertion. In the inner part, two cylindrical shell hafnium rods are envisaged to pilot the reactor both to provide poisoning or depletion compensation and to assure safety shutdowns.

Outside the core, a beryllium reflector allows to get a thermal neutron flux suitable for several test concerning fuel properties. Here neutrons coming from the centre of the reactor undergo many collisions and slow down up to representative energies to simulate LWR spectra.

In order to perform analyses of material properties, it is necessary to keep specimen temperature under control. Then a zircaloy shield is placed around half a core to reduce gamma heating in some reflector regions.

#### 1.3 JHR Experimental Capacity

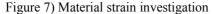

JHR material testing reactor is expected to achieve a relevant position within the framework of European research and development in nuclear technology. In order to cope with this important mission, several experimental devices have been conceived and developed for different kinds of nuclear reactors.

JHR will work under the umbrella of a nuclear facilities network to take advantage of many operative experiences all over Europe and to share important know-how. The design team and several international collaborations have highlighted the most relevant experimental needs of today industries, utilities and regulators as well as the future ones.

The challenge is to create a modern, flexible and integrated user-facility keeping the best safety standards during all the possible experimental procedures. As far as cost optimization is concerned, international market trends have been estimated to match top level performances and reactor management issues.

JHR irradiation capability is essentially twofold. Many material tests are planned to be carried out inside the core thanks to a significant fast neutron flux ranging from 2  $10^{14}$  n/cm²/sec up to 4  $10^{14}$  n/cm²/sec and a high dpa rate (from 8 to 16 dpa/year). This in-core spectrum is suitable for cladding and in-vessel components study. On the other hand, the reflector positions allow a thermal flux ranging from 5  $10^{13}$  n/cm²/sec up to 5  $10^{14}$  n/cm²/sec that may induce linear power up to 600 W/cm in 1% U235 enriched fuel samples designed for fuel property enhancement studies. In addition, even fast flux of some 7 to 8  $10^{13}$  n/cm²/sec is available in some reflector locations.

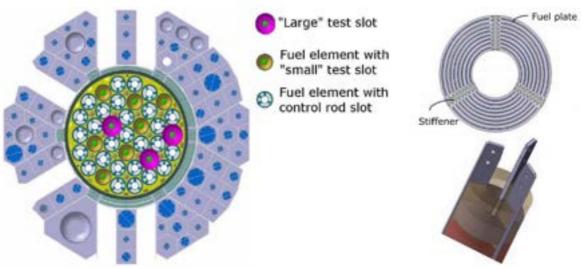

JHR experimental infrastructure takes advantage of all the facilities designed for reactor support. A large area around the core hosts a *Fission Products Analysis Laboratory* in which on-line measurements - concerning gas and liquid compounds of interest - are allowed thanks to top level instrumentation and a very close location with respect to reactor core. This reduces latency time as far as very short-lived nuclides are concerned and several activation analyses and contamination evaluations are even possible there.

Figure 3) JHR experimental areas

A <u>Dosimetry and Radioprotection Laboratory</u> is also envisaged in order to assure the best safety levels for all the operators and for further tests which may be carried out in out-of-pile environments.

Corrosion and chemical reactions are induced depending on test needs for what concerns challenging material simulations, then a <u>Chemistry Laboratory</u> is planned to support conception and performances of representative sample conditions.

JHR is also equipped with 4 <u>Hot Cells</u> to support device management since the first test stages. They are conceived for sample preparation, installation, tuning of test conditions during experiment and finally sample removal and stock. Hot cells for  $\beta/\gamma$  radiations are planned to be used for fuel test cycle operation as well as waste management. In addition, a  $\alpha/\beta/\gamma$  hot cell is expected to be used for specific contamination handling –

namely failed fuel elements or samples - coming from devices or reactor core; even cask preparation is allowed.

Figure 4) JHR core and device connections

Figure 5) JHR hot cells

Reactor piloting procedures and test staff interactions are optimized; reactor control room and device management instrumentations are designed to get closer and more interactive in order to reduce error likelihoods and improve reactor cycle utilization.

JHR device design involves several important steps starting from experimental needs identifying to the complete construction of the facility. At a first stage the experimental scenario is described in terms of irradiation conditions and possible time-dependent behaviour as well as temperature and pressure fields. Corrosion and chemical representativeness of the test are evaluated as well as mechanical stress or strain loading. Computations of neutronic and thermalhydraulic features are then performed. Cooling issues are considered both in forced and in natural convection, then interaction with core main loop is studied. After a first R&D engineering stage, all necessary equipments are taken into account concerning instrumentation and control during all the test cycle. Possibly, fission product analyses and loop contaminations are implemented and dedicated chemical and radiological devices are supplied. Connections with existing and shared facilities among JHR infrastructures are then considered in order to optimize test procedures. Hot cells and non-destructive examination benches are then integrated and manipulation risks are evaluated. Furthermore, the device design is carried out with respect to safety standards and control system management. In addition, safety analyses are performed in order to evaluate all possible device-core interactions in terms of accident and incident starting events - particularly for what concerns heat evacuation and cooling. In addition, for inpile parts all barrier tightness is expected to fit with all regulator requests.

Out-of-pile parts, electrical and hydraulic auxiliaries are then integrated with all plant tools. After this design procedure is complete, technical tests are foreseen in dedicated facilities, purchasing and component procurement are planned until device construction and operation.

JHR experimental capability is mainly aimed at representative nuclear power plant conditions. Several reactor technologies are simulated as far as thermal-hydraulic, neutronic and chemical features are concerned (PWR, BWR, CANDU, SFR, GFR, LFR, HTR, VHTR, VVER). Time-dependent power behaviour and ramps are utilized to simulate reactor transients concerning fuel samples. Accidental and incidental conditions are studied for safety purposes and regulator support. On-line radiological and chemical monitoring, as well as induced mechanical constraints, allow modern sample feature tuning and optimize control of data acquisition and quality. All these relevant enhancements in testing capability improve matching between predictive models by multiphysics computations and experimental data.

#### Core Experimental Devices

Several material tests are planned to be performed within the core thanks to a suitable fast neutron flux. About 10 experimental positions are available there for cladding and in-vessel component alloys such as

stainless steel, titanium, zirconium and nickel alloy, aluminium and control rod materials. Some tests are aimed also at chemical corrosion programs under the umbrella of European projects for nuclear material property studies.

Among these 10 test locations, 3 devices replace fuel elements and for those the maximum allowed external diameter is around 94 mm. Remaining 7 positions are in the centre of the innermost fuel plates and can host devices at most 36 mm large.

Design topics have mainly been oriented to challenging on-line multiple strain control and measurement. Material irradiation growth is evaluated by means of samples in which free blades undergo simple irradiation effects and loaded blades exhibit superimposed strains. Provided the same irradiation conditions, it is then possible to separate the effects.

Figure 6) Device for irradiation growth test

Axial stress relief is also evaluated for simple cladding and structural blades at which a previous load is imposed. Superposition phenomena are possibly investigated within gamma and neutron radiation fields. Online stress and strain control allows even dynamic tensile variations in JHR core. Creep tests regard mechanical behaviour under particular or time-dependent load. Within the framework of innovative experimental R&D, a device capable to measure and control both radial and axial stresses is under development. These two kinds of strain normally depend on geometrical dimensions and inner pressure of a cladding material specimen. Nevertheless, a device capable to set axial and bi-axial strains tuning their ratio is under development. It is expected to increase knowledge about irradiation growth effect on cladding since stress superposition issues will be investigated.

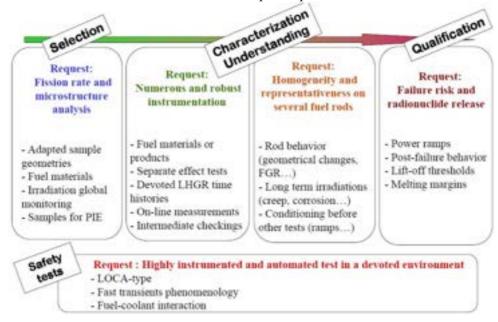

Figure 8) Simple blade stress analysis

Since mechanical properties depend on temperature and radiation conditions, it is necessary to precisely measure and control these parameters. Then several studies have been carried out to better evaluate gamma heating both through experimental tests and thanks to nuclear data enhancement. Loop thermalhydraulics has been optimized to reach suitable flat temperature profiles within the samples. For this reason, liquid metal NaK is utilized at loop temperature of about 450°C and the objective is reached since only +10°C hot spots at instrumentation contacts are present. Technical solution has been proved to be effective since very smooth axial profiles are achieved. Operational temperatures are possibly changed through electrical heaters and electromagnetic pump performances.

Furthermore, corrosion and chemical effects analyses are envisaged since device loops are possibly connected to external filtration and purification systems.

Cladding and internals materials are then analysed ranging from operative to accidental scenario configurations. JHR experimental data will be a relevant reference for selection, qualification, optimization, processing, lifetime assessment, licensing and abnormal operation tests both for safety regulators and industries.

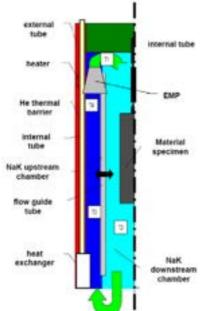

#### Reflector Experimental Devices

Fuel properties are typically studied taking advantage of thermal representative neutron spectra. In fact within JHR beryllium reflector, both fixed and moving experimental locations allow different kinds of fuel tests. Foremost, it is worth to notice that thermalhydraulic separation of device loops with respect to the core one assures safe and flexible experimental management. So it is possible to reproduce a lot of operational conditions – namely PWR, BWR, and VVER – tuning pressure and temperature parameters of the single cooling loop. HTR environments are created by means of gas circuits properly connected to chemical facilities. In addition, heavy water cooling may allow CANDU operational simulations for HWR reactor technology. JHR is so capable to support GenII and GenIII nuclear power plants as far as fuel optimization, property improvement and resources exploitation are concerned.

Single pin devices have been designed but also multiple sample locations starting from European research needs concerning Calisto loop in BR2 reactor.

Experimental configurations allow steady-state irradiations for both short and long periods, medium power transients characterized by different power ramp slopes are also envisaged. It is even possible to simulate accidental or incidental scenarios thanks to precise regulation of power generation inside the samples.

Fixed positions inside the reflector are utilized to reproduce LWR conditions, CANDU heavy water cooled and fast reactor chemical environments. Some 20 fixed slots are available with external maximum dimension of about 100 mm. One particular position may host up to 200 mm large test devices.

In-reflector slots are designed to host test samples placed on moving structures in order to modify distance with respect to the core. Here corrosion tests are expected to be carried out as well as LWR fuel studies. LOCA accidents may be reproduced as far as loss-of-coolant scenarios are concerned. High temperature reactors are interesting as well for GenIV purposes and they may be simulated even in thermal neutron spectrum conditions.

JHR reflector may host up to 6 moving structures in order to utilize linear powers up to 600 W/cm and to reproduce power ramps from nominal 200 W/cm/min up to 700 W/cm/min just changing sample distance from the core and then flux intensity within the fuel. It is possible to achieve a maximum velocity of some 50 mm/s using a test slot of about 350 mm depth.

Figure 9) JHR reflector moving structures for power ramps

It is worth to highlight that irradiation in research reactor is a necessary stage for fuel study and development. Foremost, many innovative materials are investigated through neutron radiation doses within small samples. It is now important to create homogeneous irradiation conditions and host as much specimen as possible to compare several samples, even with well-known compounds. New materials can be compared and a first selection is performed.

A second "understanding test" is carried out to obtain a precise evaluation of many physical and structural parameters taking advantage of destructive and non-destructive examinations. Knowledge about mechanical and chemical properties is deepened and operational properties of innovative fuels are then predicted.

The last irradiation concerns effective normal and abnormal operational conditions of the sample. Power ramps and long period depletions as well as abnormal transients are simulated in order to prepare, qualify and license the advanced fuels to be utilized in a nuclear power plant.

Figure 10) Innovative fuel R&D process

#### JHR Experimental Devices

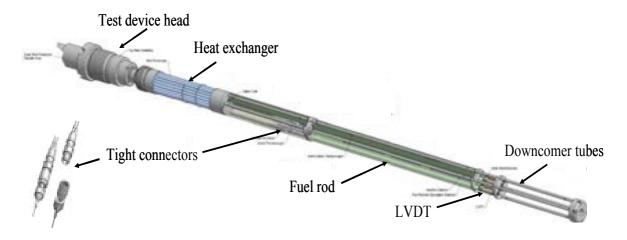

Development phases of several JHR experimental devices are carried out in order to cope with material and fuel irradiation objectives.

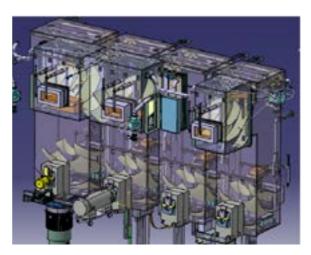

Foremost <u>CALIPSO</u> in-core test device has been conceived mainly for cladding materials investigation (in-Core Advanced Loop for Irradiation in Potassium SOdium). It is expected to be placed inside "small" in-core locations in the middle of the fuel elements to take advantage of high neutronic flux and relevant DPA rate up to some 15 DPA/y. It has been designed to achieve a uniform temperature profile between samples of the same batch through a NaK liquid metal cooled loop. In fact, maximum temperature difference is about 8°C for axial profile and about 7°C between specimens. In addition, temperature stability with respect to time is obtained. Very challenging cooling loop has been conceived as far as safety issues and confined, autonomous long period utilizations are concerned. A proper circuit allows tuning mass flow rate thanks to an electromagnetic pump placed at top of the rig (mass flow rate of some 2 m³/h and pressure drop of about 1,25 bar). In the bottom part of the device loop a heat exchanger is placed in order to remove gamma heating and to control sample temperature. Variable heat exchange surface allows twofold operating conditions ranging from 250°C up to 450°C for what concerns typical LWR operating conditions temperatures. Even higher performances are supposed to be simulated reaching 600°C with particular design configuration.

Figure 12) EM pump layout and prototype

Moreover, CALIPSO test device is planned to perform stress and strain tests allowing for on-line measurements and optimal control of experimental parameters. Sample holder design takes advantage of OSIRIS concept and expertise. Up to 5 experimental bases are embarked with 3 pre-pressurized tubular samples placed at 120° on each.

Conceptual design and thermalhydraulic analysis of critical components have been carried out and detailed study of pump and heat exchanger has been completed. Industrial procurement phase has now started and a prototype is under development.

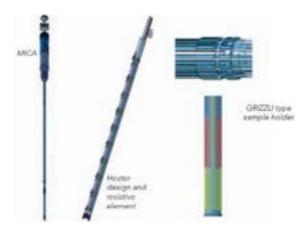

Another liquid metal cooled test device is expected to be hosted inside the JHR core - namely <u>MICA</u> (Material Irradiation CApsule). Here a NaK cooled loop is devoted to stress relief and creep analysis basically for cladding materials. Moreover, deformation and swelling analysis with on-line measurements are performed. Within this device it is possible to apply bi-axial stress to up to 10 tubular samples.

Thermalhydraulic features of a natural convection loop are utilized within a temperature range from about 200°C to around 450°C. Technological design utilized important experience from CHOUCA devices in OSIRIS material testing reactor and GRIZZLI apparatus.

Figure 13) MICA device layout

In addition, <u>MELODIE</u> experimental sample holder (MEchancal LOading Device for Irradiation Experiments) is under development. Normal and incidental conditions in LWR parameters induce fission gas release and pellet cladding interactions which lead to complex and multi-axial thermo-mechanical loadings. In order to increase fuel burnup and to get better safety features, it is necessary to obtain more reliable experimental data. Within the framework of European work package WP 1.1 program, French CEA and Finnish VTT joined the same project to realize this test device. MELODIE is expected to allow creep analyses concerning PWR cladding materials and a full on-line control of bi-axial stress; corresponding strain measurements are foreseen as well. Mechanical studies will be possible in a quite high temperature environment of about 350°C.

An improved MELODIE technology device is planned to be hosted in JHR. Design stage is completed and realization and production phase has already started.

Figure 14) MELODIE sample holder layout

JHR fast in-core neutron spectrum can be utilized also for GenIV R&D purposes. GFR technology envisages SiC/SiC composites as structural material for fuel containment. Then irradiation creep evolution at elevated temperatures combined with high fast neutron doses is a key topic in order to improve structure performances. Thus **CEDRIC** device (Creep Experimental Device for Research on Innovative Ceramic) is designed to be able to apply controlled stress for quantitative analyses and to precisely measure resulting strains. Superposition effects are investigated utilizing two samples: the first is just irradiated and the second one undergoes the same radiation dose and controlled stress at the same time. High temperature environments are simulated ranging from 600°C up to about 1000°C. A rig similar to a CHOUCA device is filled with helium gas and placed within JHR core to exploit a suitable fast flux. CEDRIC irradiation analyses have been performed inside OSIRIS reactor core. Moreover, the CROCUS device has investigated SiC/SiC bond stability with respect to SiC compound structure. In 2007 several samples have been irradiated and some important data have been obtained. Taking advantage of OSIRIS tests expertise, an improved technology will be used in the JHR.

In order to provide support in R&D for future GenIV reactor technology as well as for property enhancement of present LWR, large irradiation capacity devices are being realized within the framework of JHR project. Natural convection helium-cooled loop is under development aimed at exploiting the fast core flux through large test slots. The objective is to investigate innovative materials – namely advanced stainless steels (austenitic or ferritic steels utilized in sodium and lead-cooled technologies) or ceramics. Basically, LWR technology steels or zircalloy are interesting for such an irradiation capacity.

Figure 15) In-core large slot irradiation capability

GenIV advanced systems conceived to use innovative fuels and burn minor actinides need more precise data to R&D process support. SFR and LFR technologies are getting key concepts in future nuclear power plant fleets and thus JHR design team foresaw some experimental capabilities to cope with these challenges. Firstly evaluations have been carried out to simulate helium fission production within an Am matrix through flux, enrichment and minor actinide composition changing in order to exploit thermal flux. Helium build-up is relevant and both swelling and internal pressure make it a critical issue in fast reactor design.

Moreover, JHR test capability is expected to be oriented also towards reduction of fuel pellet data uncertainties as well as long term behaviour. Future experimental needs taken into account are also accidental simulations about innovative fuels and clad failure investigations.

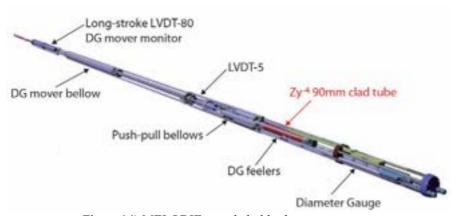

Furthermore, many experimental apparatus are devoted to fuel properties enhancement. MADISON device (Multi-rod Adaptable Device for Irradiations of experimental fuel Samples Operating in Normal conditions) is designed to perform fuel tests concerning PWR, BWR and VVER reactor technologies. It can embark 4 fuel pins (even 8 pins capacity is conceived) and reproduce normal operating conditions not aiming at clad failure. In order to exploit a proper thermal neutron flux it is placed inside the JHR reflector. Nominal reactor operation conditions are achieved also through an independent loop in which representative thermalhydraulic and chemical conditions are set up (PWR conditions achieved through pressure of some 160 bar and temperature of about 320°C). Different slow power transients are induced thanks to a moving structure whose distance from JHR core is controlled to modify neutron flux within the fuel samples. MADISON is expected to study either slow power slopes or long period irradiations (up to 3 years). Fuel material properties (microstructure, fission gas release, mechanical features...) are investigated with respect to burnup and linear heat generation rates. Clad corrosion and crack initiations are also interesting topics for long irradiation tests.

Figure 16) MADISON device layout

Very homogeneous neutron irradiations as well as high precision measurements are significant features of this device. Nominal linear power envisaged is about 400 W/cm simulating high burn-up fuels by means of 1% U235 enriched UO<sub>2</sub> samples.

MADISON is going to perform different kind of experiments:

- selection tests to irradiate and compare innovative samples

- characterization tests to irradiate few samples and to obtain many physical information

- qualification and validation tests to reproduce reactor operative conditions

This device is capable to utilize several JHR facility apparatus and examination tools.

MADISON design takes advantage of important collaborations between French CEA and IFE Halden expertise which started from domestic know-how to reproduce in JHR an innovative and challenging loop. Design and feasibility phases are completed; realization and manufacturing stages are ongoing.

Moreover, <u>ADELINE</u> in-reflector experimental device is conceived in order to perform single LWR fuel pin tests concerning up to limit and incidental scenarios. It is hosted on a moving structure and several power ramp tests take advantage of the ISABELLE1 device expertise in OSIRIS reactor. Rod internal overpressurization and free gas sweeping, as well as fuel centre melting approach, are investigated since clad failure configuration is allowed in this apparatus. Then precise measurements in clad failure timing and linear heat generation rate related to incidental situations are achieved in this device.

Moreover, normal conditions after clad failure are envisaged since the loop is designed to operate with contaminated coolant. Fission gas release during transients is detected by Fission Product Laboratory instrumentations through on-line gamma spectrometry and delayed neutron detection techniques. In addition, permanent purifications and radiology controls are performed on the out-of-pile part of the loop. In order to limit the amount of contaminated coolant a jet pump is installed inside the device. The thermalhydraulic and chemical representative environment are achieved for what concerns failure simulations.

ADELINE apparatus is placed on reflector moving structure to set thermal flux and then power levels. Typically both PWR, BWR and VVER technologies are studied and either UO<sub>2</sub> 12% 235U enriched fuel or MOX 20% Pu/(Pu+U) enriched fuel are utilized.

Moving structure allows power ramps and a sample test transient may induce a first irradiation plateau (1 day up to 1 week) at a linear power of some 100 W/cm; then a ramp is induced ranging from 100 W/cm/min up to 700 W/cm/min. Furthermore a high power plateau is kept for about 24 hours at about 620 W/cm. As explained before, the facility design allows withstanding clad failure during this procedure.

Figure 17) ADELINE loop layout

**LORELEI** experimental device (Light water One Rod Equipment for LOCA Experimental Investigations) is designed to investigate LOCA transients. Basically thermalhydraulic aspects, radiological consequences and mechanical issues of this kind of accident are the objective of foreseen simulations. Since this device is located on a moving in-reflector test slot, power level is expected to be controlled and independent loop assure safety requests to be respected. LORELEI design is aimed at understanding of ballooning and burst of cladding materials and corrosion phenomena in elevated temperature environment.

Simulation scenarios take into account a first depletion phase in order to create a representative fission products inventory within the fuel matrix.

Then a dry-out phase through gas injection is devoted to start the loss of coolant. Steam is produced thanks to evaporation of some liquid water in the bottom part of the device.

Power is tuned by means of device displacing and a homogeneous temperature profile is reached through both several electrical heaters and a screen to flatten the neutron flux.

Fission Product Laboratory is always connected to the loop to perform on-line radiological and chemical analyses about the test evolution.

This device design is based on GRIFFON apparatus which has been operated inside the SILOE reactor under the umbrella of the FLASH Program for LOCA accidents.

Finally, **OCCITANE** experimental device (Out-of-Core Capsule for Irradiation Testing of Ageing by NEutrons) is devoted to steel analysis and investigations. Since vessel is a critical component for a nuclear power plant and a barrier according to defence-in-depth safety approach, it is necessary to qualify material features to prove their lifetime within a neutron radiation field. OCCITANE technology is based on IRMA device which is located in OSIRIS reactor. Irradiation is performed in an inert gas atmosphere and a temperature of some 230°C to 300°C is expected. On the other hand, dose rates of some 100 mdpa/y are envisaged. Optimization phase is now concerned with best location within the reflector slots. Temperature control is a key point and a thermal and mechanical simulation study is going on.

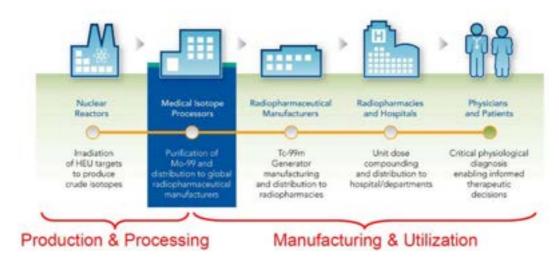

#### JHR Irradiation Devices for Medical Purposes

Medical radioisotopes production and procurement is becoming a more and more strategic issue within the framework of worldwide healthcare system. Nuclear physics application has allowed precise imagining and effective therapies for twenty years. Nuclear medicine diagnostics involves several kinds of radiation and procedures taking advantage of unstable artificial nuclei undergoing decay. In this branch of medicine, the most important radioisotope is Technetium-99m and it is used nowadays in around 20 millions diagnostic procedures: half of them are bone scans, and the remaining half is roughly divided between kidney, heart and lung scans. This radionuclide is suitable for medical imaging since it has got a half-life of about 6 hours which is low enough to allow the patient to leave the hospital after short delay. Conversely the half-life of the parent nuclide – the Molybdenum-99 – is some 66 hours long enough to be transported from the processing sites to the end user facilities.

Therefore Technetium-99m supports around 85% of nuclear medicine diagnostics and then Molybdenum-99 (Mo99) production and stock are key issues in worldwide healthcare management.

Figure 18) Molybdenum-99 production and utilization

Within a European framework, a research reactor network assures Mo99 stocks for hospitals and medical processes. Recent 2008 and 2009 crisis in Mo99 supply highlighted the need for an infrastructure optimization concerning transportation, stock and management. On the other hand, it has been possible to realize the importance of joint efforts performed by multipurpose material testing reactors and their vital role in providing radioisotopes.

Since the construction of an industry owned Mo99 production dedicated reactor has failed in Canada (MAPLE project), European NEA and OECD strategies have envisaged restoring the existing research reactor infrastructure managed by public bodies and networked in order to assure proper spare production. In fact, European market is conceived as a multi-line backup system. Conversely other local markets – namely Australia, Canada and South Africa – are single-line structured and less able to prevent or face supply shortage.

European research reactors construction started before a significant diffusion in nuclear medicine diagnostics and then overcapacity has always allowed the market to keep the prices low. People in Europe accessing these diagnostics have increased up to 9 millions. Thus it is necessary to ensure future production provided that short term availability of these facilities is compromised due to temporary maintenance and extended time scale in replacement of ageing existing research reactors.

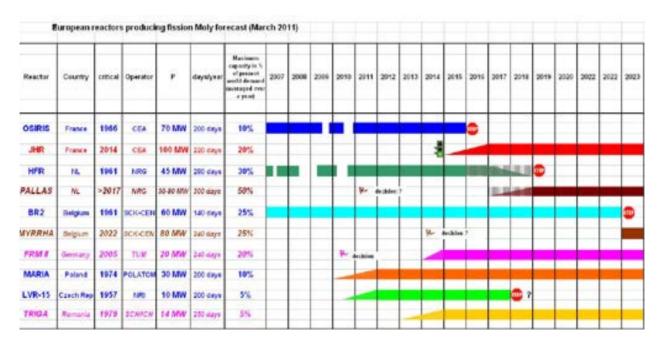

European production network was formed until recently by 3 reactors:

- BR2 (Mol, Belgium) is a multipurpose research reactor operated by SCK-CEN and it is expected to leave service by 2023.

- HFR (Petten, Netherlands) is a multipurpose research reactor owned by European Commission and operated by NRG, it is expected to leave service by 2018.

- OSIRIS (Saclay, France) is a multipurpose research reactor operated by CEA and it is expected to leave service in 2015.

Recently, two facilities joined this infrastructure in order to enhance production:

- MARIA (Otwock-Swierk, Poland) is a multipurpose research reactor operated by Institute of Atomic Energy POLATOM which started production in 2010 and is expected to achieve around 50% of European needs by 2012).

- LVR-15 (Rez, Czech Republic) is a multipurpose research reactor refurbished in 1989 and operated by RCR. It is expected to be operated until 2029 at least.

Operating lives and shutdown timetable are strictly demanding for reactor replacement and future European scenarios are planned in order to assure Mo99 supply system.

- FRM (Munich, Germany) is a new research reactor operated by TUM since 2005 which is supposed to reach peak production around 60% of European demand

- TRIGA (Pitesti, Romania) is a multipurpose research reactor operated by INR until 2030.

- JHR (Cadarache, France) is going to be a new material testing reactor under construction and it will be operated by CEA. It is expected to reach criticality in 2016 and to be able to supply about 35% of European need up 50%.

- PALLAS (Petten, Netherlands) is a multipurpose research reactor to be operated starting from 2017 by NRG to replace HFR

- MHYRRA (Mol, Belgium) is designed to be an accelerator driven system (ADS) scheduled to be operated by SCK-CEN from 2022 in order to face to 100% of European demand.

Several facilities are supposed to face increasing in European Mo99 need provided that some 200%/250% of market demand has to be guarantee by total peak generations. It is necessary to be able to withstand unexpected plant shutdowns or planned maintenance. In addition, it is useful to get a backup capacity in order to supply other regional process lines all over the world.

Figure 19) Research reactor replacement timetable

Figure 20) Evolution in percentage supply of Mo99 European demand (%)

In this critical and strategic European scenario concerning healthcare system, research reactors play an important role to secure public issues. A more and more collective and networked approach is envisaged to fit with demand and guarantee operational flexibility in order to maintain low prices and fair trade market. Replacing ageing reactors and add a significant generation capability to facility network will increase reliability and will strengthen European procurement and stock capacity.

JHR is also expected to become a very important keystone even in this framework. It is planned to contribute to a nuclear research infrastructure which is capable to share experimental capacity and high level technological facilities for the benefit of European community. Progress in nuclear science is getting more and more present in everyday life and research reactors have got prepared to match with all these challenging scenarios.

#### 2 Research Description

#### 2.1 Thermalhydraulic and Neutronic Core Model

Power transient analyses of nuclear reactors are very important design steps in order to study the evolution of temperature in many significant components during shutdown, start-up or regulation phases. In fact, material resistance and mechanical properties strongly depend on temperature. Mainly, fuel and cladding heating are controlled to prevent them to melt and then release some radioactive nuclides into the cooling loop. Safety defence-in-depth envisages the integrity of fuel matrix and cladding shell as first and second barrier against leakage of radioactive fission products.

Power transients during reactor shutdown are particularly evaluated in the present analysis. Energy release throughout the core depends on neutron and gamma radiation transport but basically the power source is related to fission reaction rate in fissile material – namely the fuel.

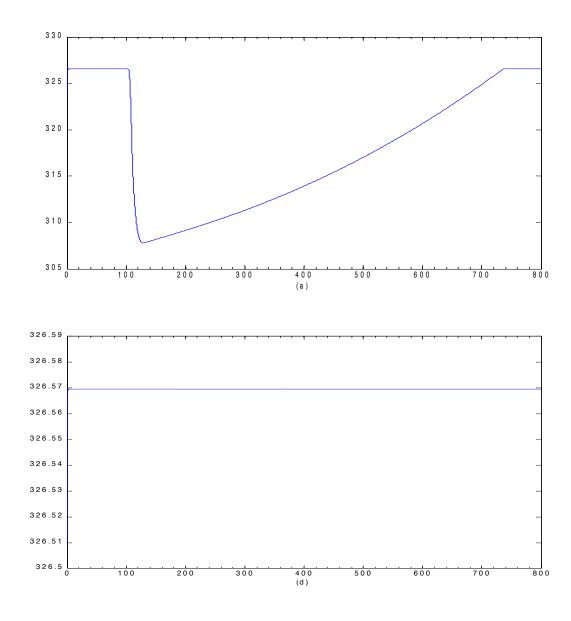

Control rod insertion causes an increasing in neutron absorption due to the hafnium tendency to neutron capture. It induces a reduction in neutron population within the system at a time scale compared to mean generation time of prompt neutrons. Consequent temperature drop has neutronic feedbacks related to Doppler broadening, moderation and absorption changes. Then, neutron kinetics requires a coupled thermalhydraulic and neutronic analysis of the system in order to account for these interactions. For this purpose, the DULCINEE kinetics code is utilised. It has been developed by the French Institute of Radiation Protection and Safety (IRSN) and it computes power evolution according to pointwise neutron kinetics approach.

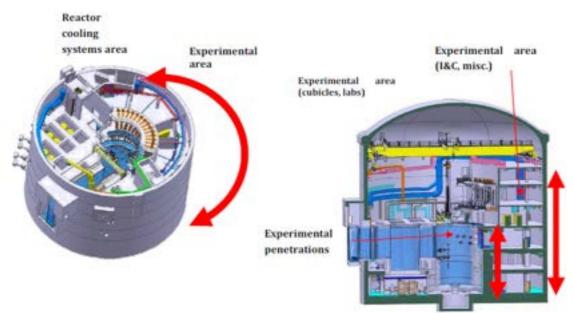

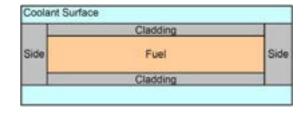

Foremost, a representative thermal model has been conceived in order to well describe the temperature evolution within the fuel, the cladding and the coolant. Providing separation of variables and computing energy conservation for average temperatures in fuel, cladding and coolant, physical similarity is reached coherently with the need for a correct time behaviour description. Then JHR fuel equivalent plate has been simulated both considering the average fuel element and the hottest plate in the core.

Figure 21) JHR fuel plateFigure 22) JHR model plate

| Fuel meat length [mm]                    | 63.35  |

|------------------------------------------|--------|

| Fuel meat thickness [mm]                 | 0.61   |

| Cladding thickness [mm]                  | 0.38   |

| Plate side thickness [mm]                | 8.42   |

| Fuel plate height [mm]                   | 600.00 |

| Hydraulic diameter [mm]                  | 3.71   |

| Wet perimeter [cm]                       | 16.40  |

| Fuel volume [cm <sup>3</sup> ]           | 23,18  |

| Cladding volume [cm <sup>3</sup> ]       | 28.88  |

| Plate sides volume [cm³]                 | 13.83  |

| Coolant volume [cm <sup>3</sup> ]        | 91.25  |

| Fuel/cladding surface [cm <sup>2</sup> ] | 760.17 |

Table 1) JHR model plate dimensions

| Cooling mass rate [kg/s]      | 1803 |

|-------------------------------|------|

| Coolant inlet temperature[°C] | 30.0 |

| Core inlet pressure [bar]     | 9.3  |

| Core outlet pressure [bar]    | 6.3  |

| Core pressure drop [bar]      | 3.0  |

Table 2) JHR core boundary conditions

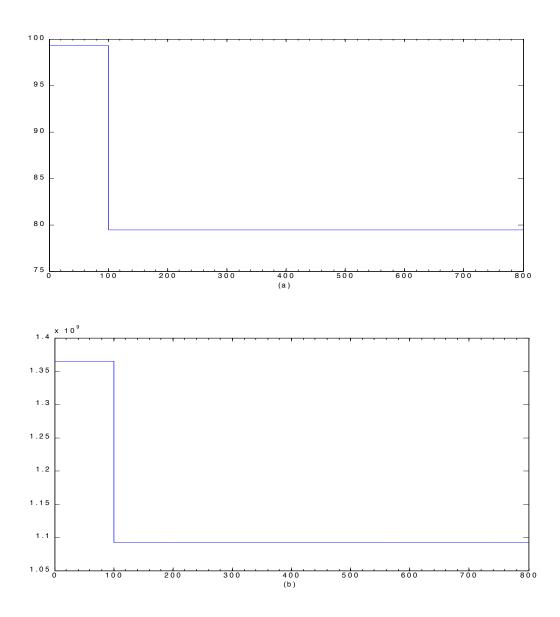

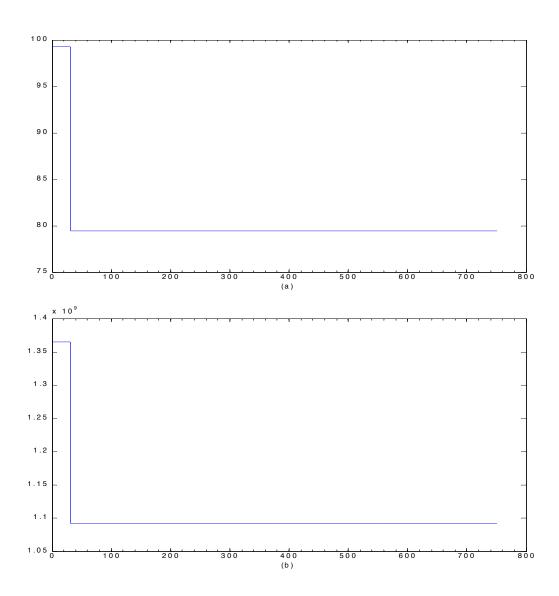

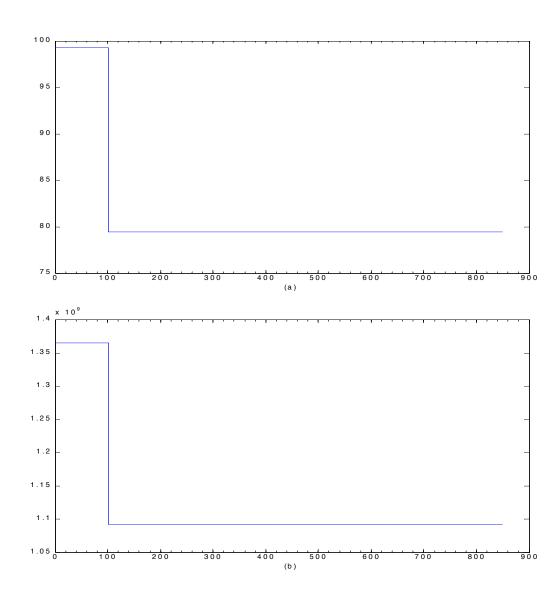

Moreover, the neutronic parameters of the system account for the delayed neutron fraction, the mean neutron lifetime and the time constants of neutron precursor groups. Fuel composition changes due to fission products poisoning and burnup of heavy nuclei. As far as related effect on neutron kinetics, the equilibrium cycle has been divided into four steps: Beginning of Cycle (BOC), Xenon Saturation Point (XSP), Middle of Cycle (MOC) and End of Cycle (EOC).

The following table shows a negligible Pu239 build-up which induces delayed neutron fraction to remain quite constant as well as delayed contributions related to precursor groups; deterministic APOLLO-MOC calculations have evaluated neutron lifetime around 40 µsec.

|                      | BOC   | XSP   | MOC   | EOC   |

|----------------------|-------|-------|-------|-------|

| BURNUP [GWD/ton]     | 44.81 | 47.02 | 59.19 | 74.67 |

| Beta effective [pcm] | 720   | 718   | 712   | 705   |

| Doppler [pcm/K <sup>1/2</sup> ] | - 2.94                 |

|---------------------------------|------------------------|

| Void [pcm/m <sup>3</sup> ]      | - 4.53 10 <sup>5</sup> |

| Moderator [pcm/K]               | - 19.5                 |

Table 3) Equilibrium cycle compositions

Table 4) Feedback coefficients

|                         |          |     | В     | eta Fra | ction | 15                   |     |                       |            |

|-------------------------|----------|-----|-------|---------|-------|----------------------|-----|-----------------------|------------|

| Group 1                 | Group 2  | Gr  | oup 3 | Grou    | p 4   | Group                | 5   | Group 6               | Beta eff.  |

| 0.0404 \$               | 0.1795 S | 0.1 | 743 S | 0.379   | 68    | 0.0837               | S   | 0.1427 S              | 1.0000 S   |

| Lambda 1                | Lambd    | a 2 | Laml  | bda 3   | La    | mbda 4               | L   | ambda 5               | Lambda 6   |

| 0.01330 s <sup>-1</sup> | 0.03250  | 5   | 0.121 | 82 s'   | 0.3   | 1651 s <sup>-1</sup> | 0.5 | 98880 s <sup>-1</sup> | 2.94956 s' |

Table 5) Neutron kinetics parameters

Finally the thermal effects of the system are related to neutronic description through reactivity feedback coefficients. Then it is possible to consider Doppler effect and change in moderation due to void or coolant dilatation.

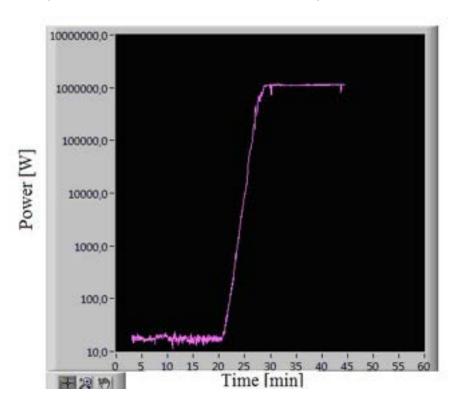

DULCINEE code has allowed modelling JHR as far as thermal features are concerned and feedback relations impact on neutron kinetics. Once pointwise kinetics model has been solved, power transients have been evaluated.

#### 2.2 Shutdown Systems for JHR

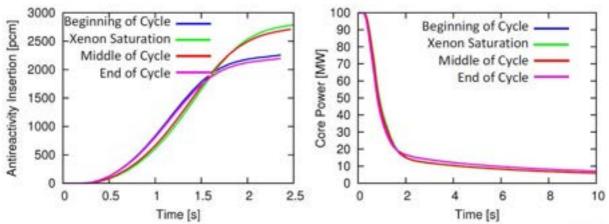

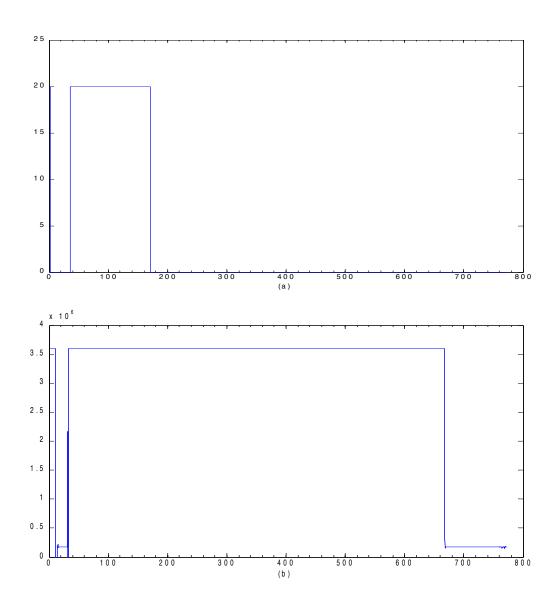

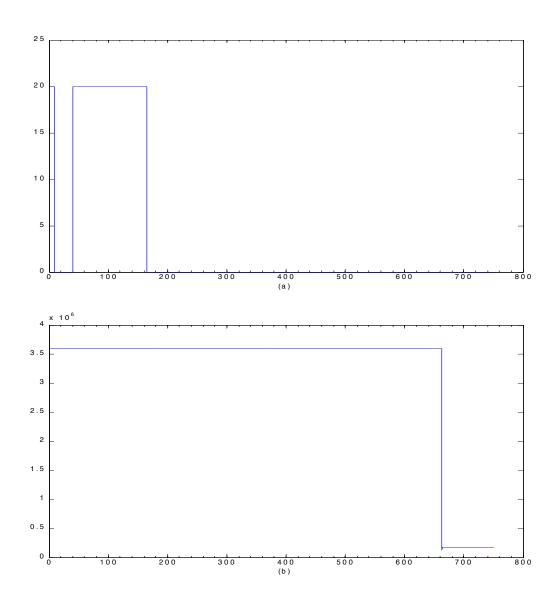

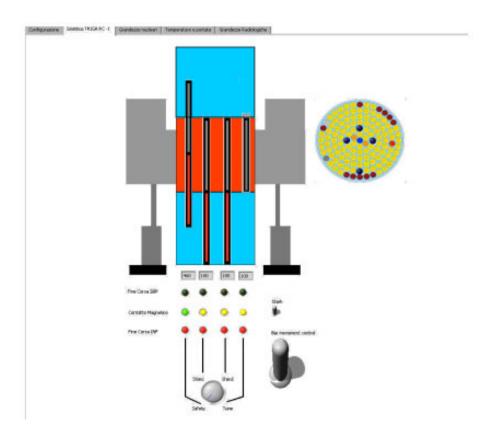

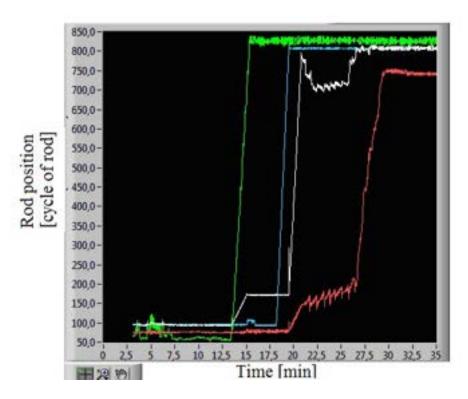

In the present analysis only power transients during shutdowns are considered. JHR safety approach envisages two different shutdowns for reactor piloting – namely Normal Shutdown (NS) and Safety Shutdown (SS). As explained before, JHR is equipped with 27 control rods for core poisoning compensation, reactor piloting and emergency shutdown. A group of 19 Compensation Rods (CR) is designed to one by one withdrawal throughout the cycle to provide extra reactivity and assure system criticality. Moreover, a 4 Pilot Rods (PR) bank is kept as close as possible to the core mid-plane in order to take advantage of the highest differential worth. Remaining 4 Safety Rods are clustered in a bank as well and completely extracted from the core during normal operations.

Normal Shutdown utilizes just the Pilot Rods bank and the injection starts from criticality position until core bottom. Since this initial insertion depends on fission product poisoning, antireactivity introduced by control devices changes during reactor cycle as well as insertion speed. Then Pilot Rods worth may change from some 2200 pcm up to 2700 pcm.

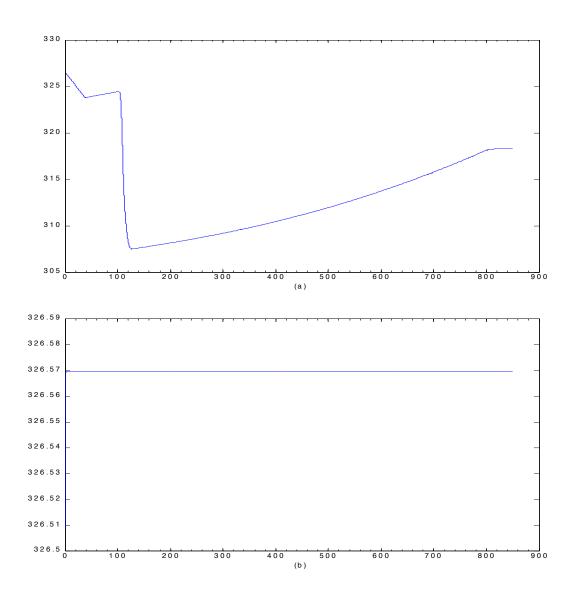

By means of the DULCINEE code, thermalhydraulic coupling with control rod antireactivity insertions has allowed to compute the Normal Shutdown power transient.

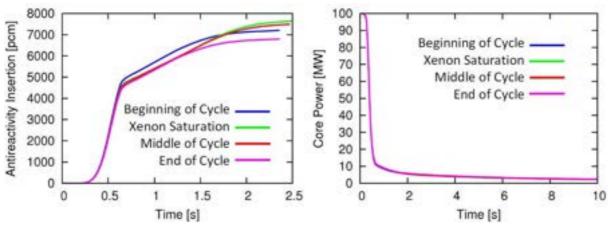

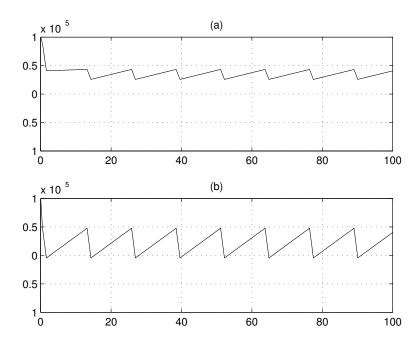

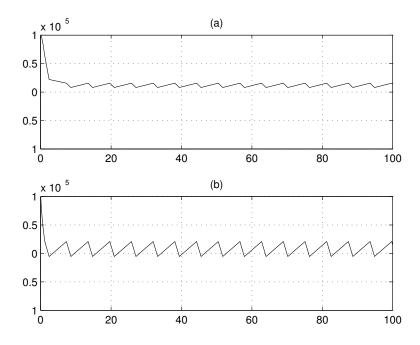

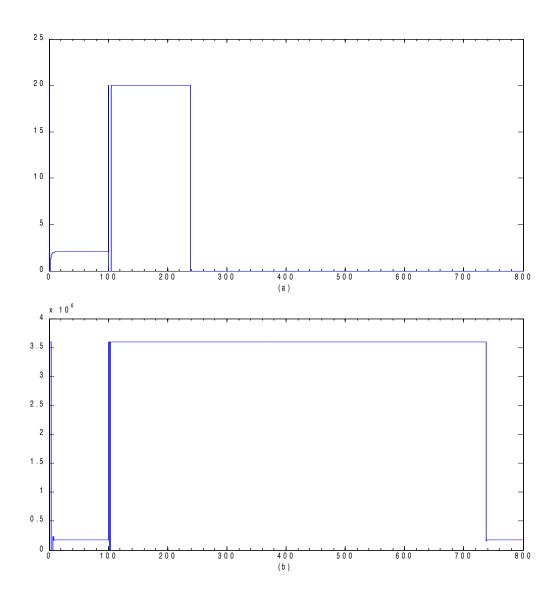

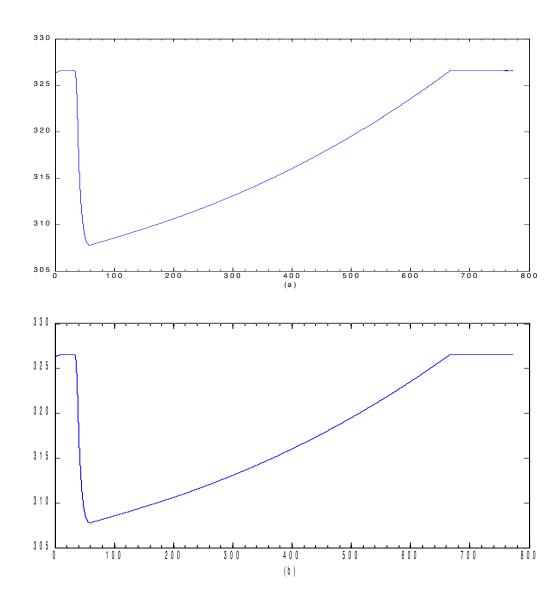

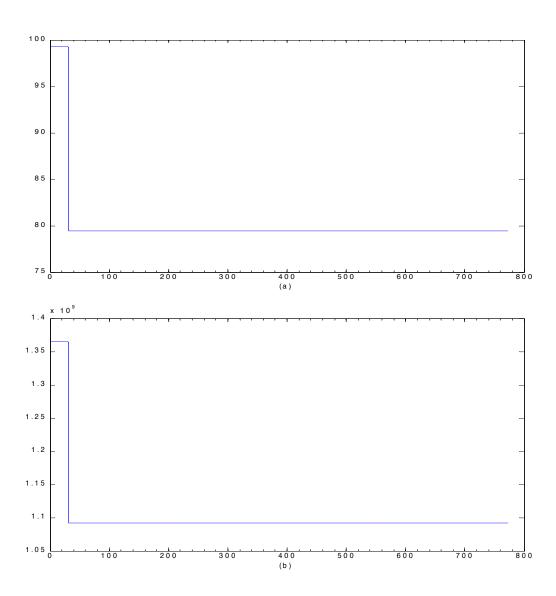

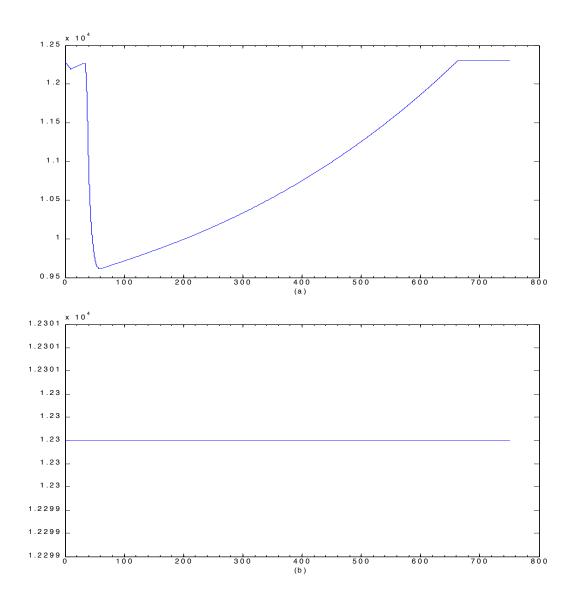

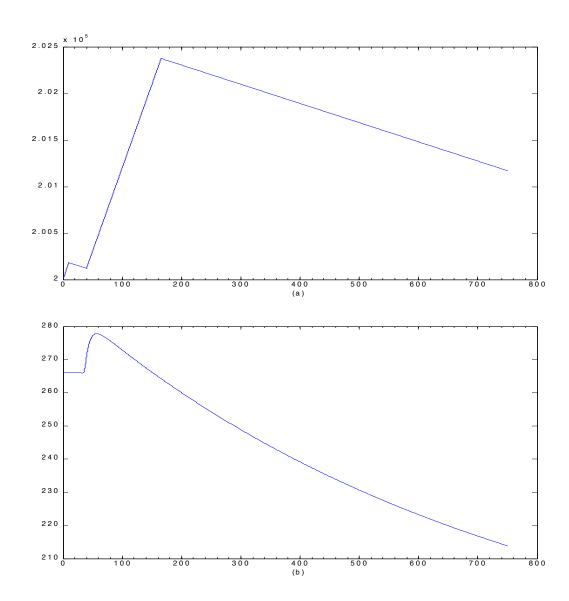

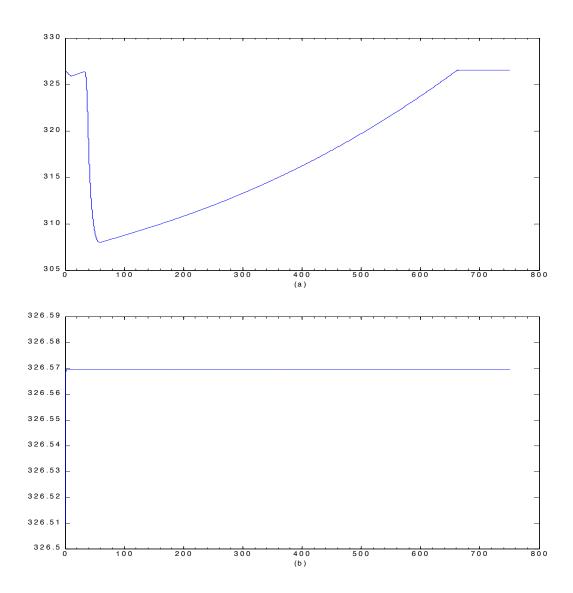

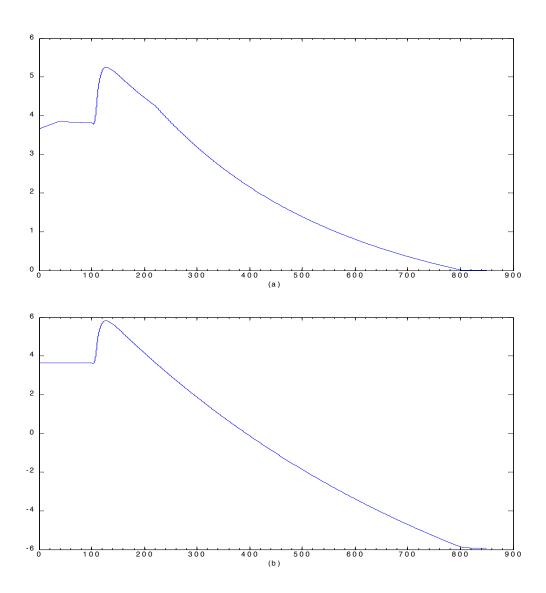

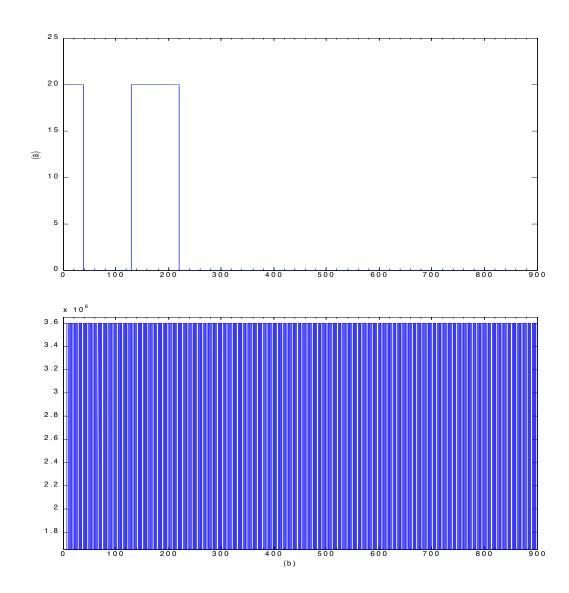

Figure 23) Normal Shutdown antireactivity injection

Figure 24) Normal Shutdown power transient

On the other hand, Safety Shutdown has been conceived to provide a higher amount of antireactivity and it employs both the Pilot Rods and the Safety ones. It is a Normal Shutdown with a complete Safety Rods insertion at the same time from top of the core in just 1.23 sec.

As shown in the previous case, even power transient during Safety Shutdown has been evaluated.

Figure 25) Safety Shutdown antireactivity injection

Figure 26) Safety Shutdown power transient

#### 2.3 Core-Reflector Coupling

JHR fast core spectrum sustains nuclear chain reaction and neutrons getting out of the central region towards the reflector undergo fission within the test samples. So there is a strong coupling between these two reactor parts that is worth to consider during transients.

If absorbing materials such as control rods are inserted into the core, the flux shape changes and then it exhibits a significant dependence on their position, even reduced power causes flux amplitude to decrease.

The propagation of core flux decrease occurs throughout the reflector with a twofold time scale. Foremost the prompt neutron lifetime – about 40 microsec – is the order of magnitude of about 90% of reactor thermal power. This sudden reduction can be thought of as immediate compared to control rod kinetics.

On the other hand, delayed neutron production time scale goes from some tenths of second up to about 50 sec, depending on precursor group. They account for at most 1% of total power and they continue to be produced according to neutron precursors decay laws. It is a sort of intrinsic power generation capacity of irradiated fissile materials and it has to be evacuated by the coolant loops for a period of time which is proportional to initial power level.

Both prompt and delayed neutron generations are present within reflector fuel samples. So this double time scale in neutron supplying to devices has to be thought of as overlapped with local multiplication. The latter causes a delay superposition which affects power production in specimens.

A precise evaluation needs particular neutron kinetics issues to be taken into account during shutdown analyses. On the other hand, a complex geometric domain requires the utilization of Monte Carlo 3D codes to properly consider core-reflector interactions, provided a lack of useful symmetries.

Code state of the art in Monte Carlo techniques doesn't allow the user to perform time dependent calculations related to variations concerning geometry or compositions. In fact, multiphysics analyses related to thermal, mechanical or domain shape feedbacks are still under development by several software and code within the framework of international projects. So it is not currently possible to account for a neutronic source with changes with respect to time due to control rods insertion. It is not even possible to properly evaluate the neutron irradiation received by the samples under the absorber induced flux shape modification. Then TRIPOLI 4.8 Monte Carlo transport code has been utilized to compute neutron flux distribution with

Then TRIPOLI 4.8 Monte Carlo transport code has been utilized to compute neutron flux distribution with static calculations all over the reactor and the reflector. This code has been developed by French Atomic Energy Commission (CEA) and it solves transport equations utilizing a statistical approach to integral equations taking advantage of a large number of particle simulations by means of parallel computing.

Normally, neutron transport techniques take into account the static solution related to Boltzmann equation coupled with neutron precursor group decay.

Provided  $\varphi(\vec{r}, E, \Omega, t)$  the neutron flux depending on space phase – namely geometric position, velocity and direction – it changes with respect to time as follows:

$$\begin{cases} \frac{1}{v} \frac{\partial \varphi}{\partial t} = -G\varphi - \Sigma\varphi + \Sigma_s \varphi + M_p \varphi + \sum_i \lambda_i C_i \\ \frac{\partial C_i}{\partial t} = -\lambda_i C_i + M_{R_i} \varphi \end{cases}$$

These equations, coupled with usual boundary conditions, rule evolution of neutron flux with respect to time. The first takes into account a balance between geometrical leakage (G), absorption and out-scattering ( $\Sigma$ ), in-scattering ( $\Sigma_s$ ) and prompt neutron production ( $M_p$ ). The last sum provides delayed neutron contributions. On the other hand, the second equation rules the build-up of neutron precursors due to delayed production term ( $M_R$ ).

Supposed a time independent problem, derivatives are turned to zero and the previous equation, always coupled with proper boundary conditions, yields:

$$k L \varphi = \left( (1 - \beta) \chi_p + \sum_i \chi_{R_i} \beta_i \right) M \varphi$$

The effect is to compute the neutron production throughout a fissile material considering a weighted generation spectrum which influences all nuclear reactions. This holds at constant power during nominal operation when the ratios between the delayed neutron populations and the prompt one are constant and equal to beta fractions. During shutdowns which take about 1 or 2 sec, prompt neutron population decreases very quickly but delayed neutrons continue to be injected into the system by means of precursors decay.

Static calculations evaluate just flux shape related to a constant neutron production which corresponds to a virtual constant reactor operation for every given control rod insertion.

Monte Carlo code gives results that need to be normalized compared to meaningful integral values of the system, typically the total amount of fission reactions which is well defined either in nominal or in dynamic analysis.

DULCINEE shutdown transient evaluations provide the total core power with respect to control rod positions and time. Therefore TRIPOLI 4.7 static calculations have been coherently normalized conserving the total amount of fission reactions.

On one hand conservation of the intensity of the flux is respected, on the other hand prompt-to-delayed neutron fraction is overestimated during shutdown due to Monte Carlo approach. This effect simulates a more energetic neutron population with a higher likelihood to get out of the core and then to reach the reflector devices.

Even neglecting effective energy distribution in neutron flux, a more conservative spectrum is considered and then a better evaluation for what concerns safety issues is obtained.

Since the objective of the present study is the power release in reflector devices, it is worth not just to consider flux shape but also fission reaction rate distribution.

In addition, even fission products kinetic energy is the most important contribution to power deposition; neutrons and gamma radiation are significant energy carriers. The first ones undergo scattering reactions and absorption generating gamma rays, gamma photons heat up metals and structures due to attenuation processes.

So it is not possible to consider that all the amount of energy released is deposited at the same place since it diffuses depending on particular radiation transport laws.

In order to take also into account the core contribution to reflector device heating for radiation leakage, energy deposition calculations are suitable in order to be coherent with physical phenomena.

Gamma radiation is created during fission process and it leaves the site diffusing all around from about 10<sup>-14</sup> sec and 10<sup>-7</sup> sec after the reaction, then it is called prompt gamma radiation. Unstable fission products usually decay in several ways, often they emit gamma photons even with time scale longer then fission ones, typically of the order of 10<sup>4</sup> sec. Activated nuclei undergo gamma emissions as well, and all these are called delayed gammas.

TRIPOLI code doesn't perform material evolution calculations and it can take into account just the prompt gamma radiation.

Then Monte Carlo analysis has considered neutron contribution in energy deposition – namely scattering and fission products kinetic energy – and prompt gamma heating to materials.

#### 2.4 Reflector Device Calculations

Since in-core neutron spectrum is quite fast, several test requiring thermal irradiations are performed inside the beryllium reflector taking advantage of its capability in slowing down neutrons. As explained before, fuel properties are studied for different irradiation levels and with different power ramps simulating various operation conditions.

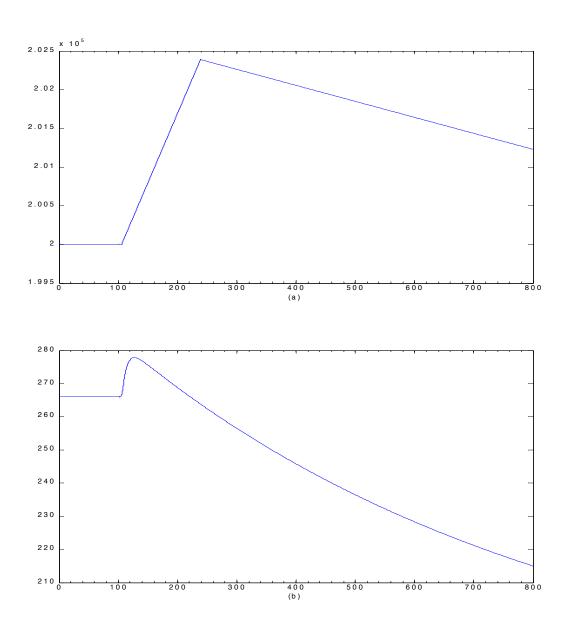

MADISON test device has been designed to perform fuel irradiation in order to reproduce nuclear power plant normal operations. It will be placed on a moving structure which will be able to set neutron flux properly tuning the distance from the core centre. Normally, it is expected to be loaded with 4 uranium dioxide 1% U235 enriched fuel pins aiming at relatively high burnup fuel simulations.

ADELINE experimental device is aimed at post-failure and abnormal operation conditions studies. It will host just 1 fuel pin (UO<sub>2</sub> 1% U235 enriched) and it is expected to perform power ramps up to material limits and simulate normal conditions after partial cladding damage.

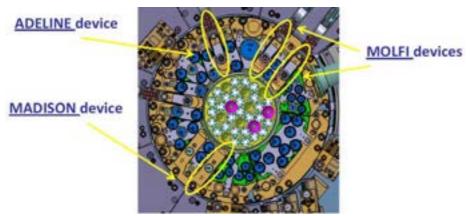

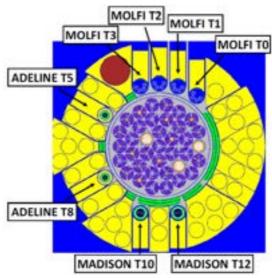

Moreover, MOLFI device is placed within the reflector but it is devoted to radioisotope production for medical purposes. Molybdenum 99 is obtained by means of U235 fissions. For that, several AIU targets are put on moving structures to be irradiated and to achieve Moly99 build-up. An example of core and reflector configuration is shown in the picture below.

Figure 27) JHR core and reflector devices configuration

Regarding in-reflector test devices, cooling is provided through independent loops designed to be flexible and to reproduce many reactor thermalhydraulic conditions (PWR, BWR).

Safety approach and procedures require power generation evaluations during transients since it is mandatory to control fuel temperatures even for what concerns fuel samples inside experimental in-reflector devices.

As piloting is achieved by means of core control rods, it is necessary to evaluate the reflector devices response to manage their power transients during reactor shutdowns. In addition, if safety temperature thresholds are reached in some fuel loaded samples, it is worth to know their power behaviour and then the related kinetic delays which occur during consequent reactor shutdown. Therefore it is necessary to aim at neutronic coupling description between core and reflector considering absorber insertion effects.

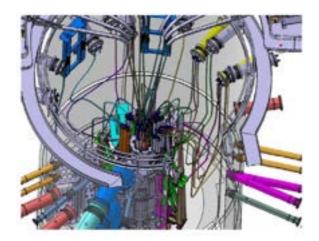

The Monte Carlo model to evaluate energy deposition and then power transients in JHR reflector devices consists of 4 MOLFI devices, 2 MADISON and 2 ADELINE test samples. Different reflector locations are considered for the same experiment aiming at location effect investigation.

Moving structure allows device displacement but the configuration in which the samples are close to the core has been considered since it corresponds to the highest core-reflector coupling.

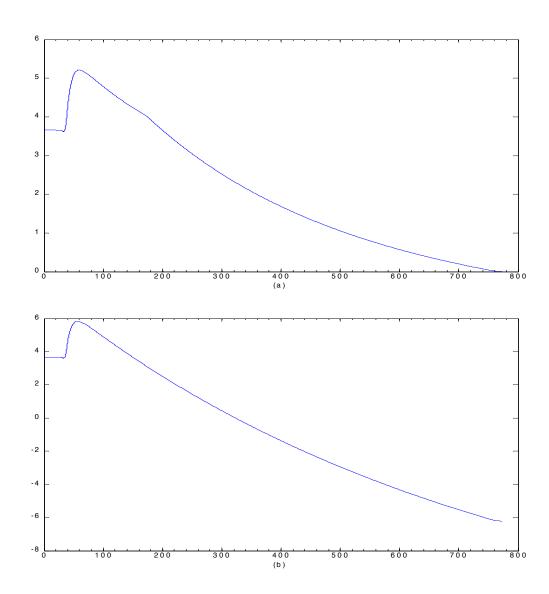

A simplified analysis considers device power proportional to core power through a time dependent coefficient. This accounts for delays and flux shape modifications. In order to be conservative, power coupling have been evaluated just for nominal configuration and complete control rod insertions after both Normal Shutdown and Safety Shutdown.

The implemented TRIPOLI model is showed in the following picture.

Figure 28) TRIPOLI model for JHR core and reflector

These coefficients refer to energy deposition calculations which take into account neutrons and prompt gamma radiation as well. Such a criterion accounts for radiation transport and basically gamma diffusion.

These ratios have been treated and for every device the coefficient corresponding to the highest power level has been kept as constant during the entire transient. Needless to say, the most conservative configuration corresponds to complete control rod insertions. In fact, the flux shape exhibits significant peaks within reflector fissile samples due to absorber injection in the core.

Therefore an evaluation related to the asymptotic composition has been used even during the very first part of the transient. So starting power is overestimated and safety issues are respected.

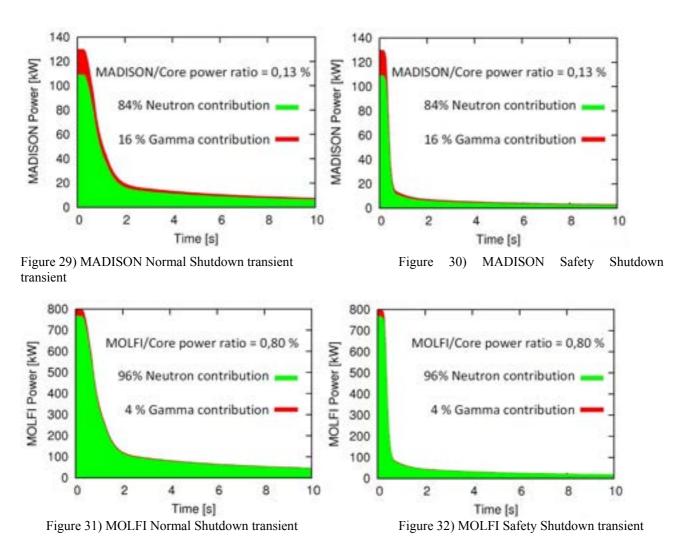

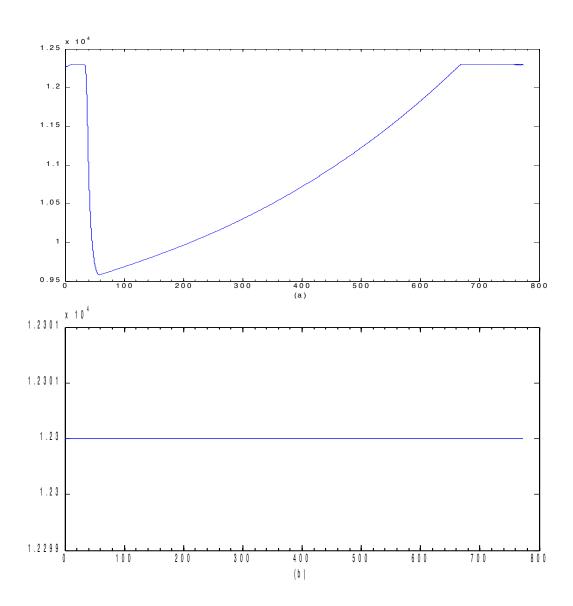

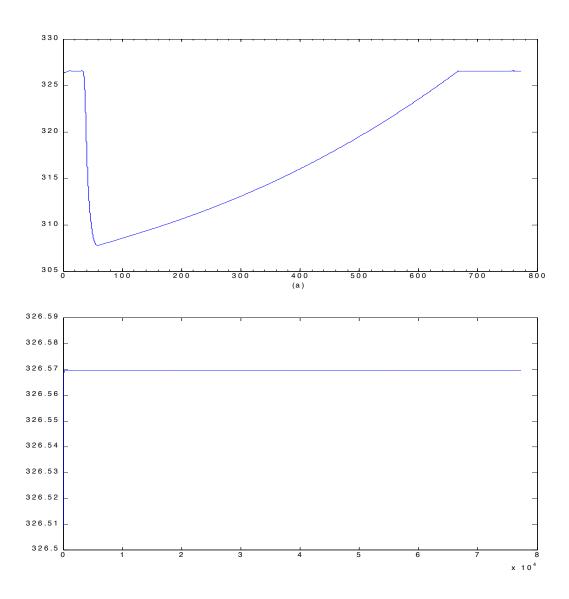

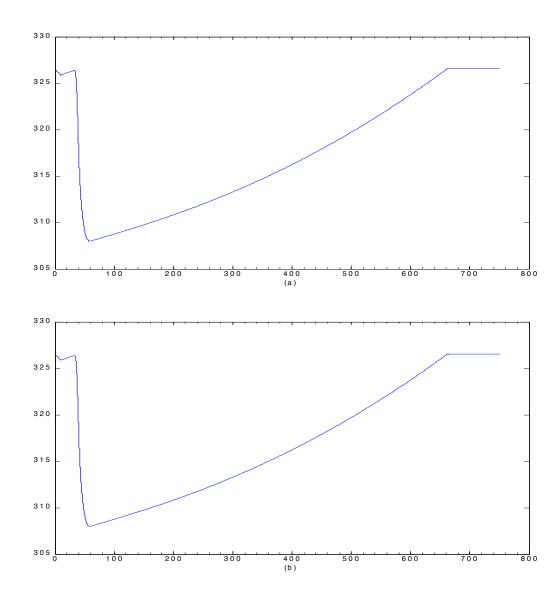

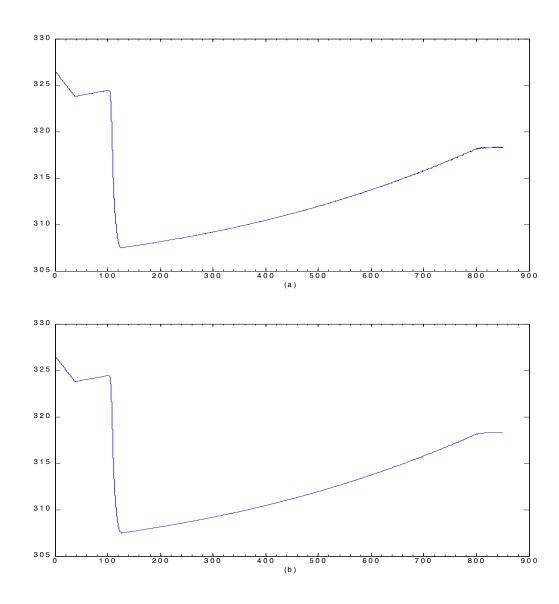

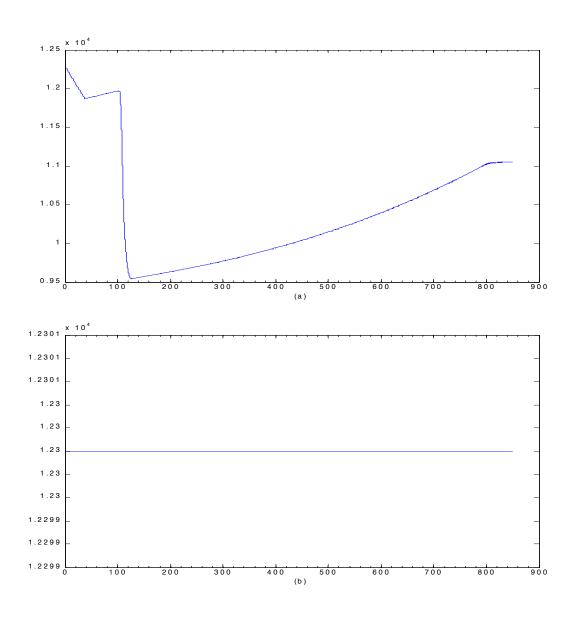

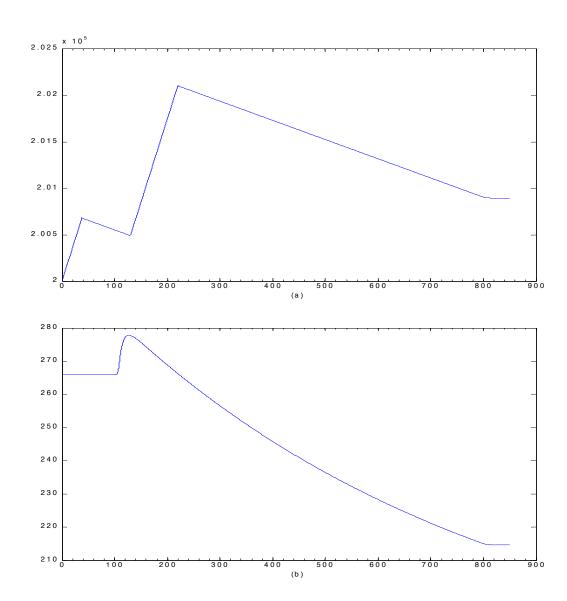

Finally Normal Shutdown and Safety Shutdown power transients have been evaluated for every reflector device through TRIPOLI energy deposition coupling coefficients and DULCINEE core transients. BOC and EOC power profiles have been considered regarding Normal Shutdown since they are more conservative. On the other hand, average profile has been implemented for Safety Shutdowns.

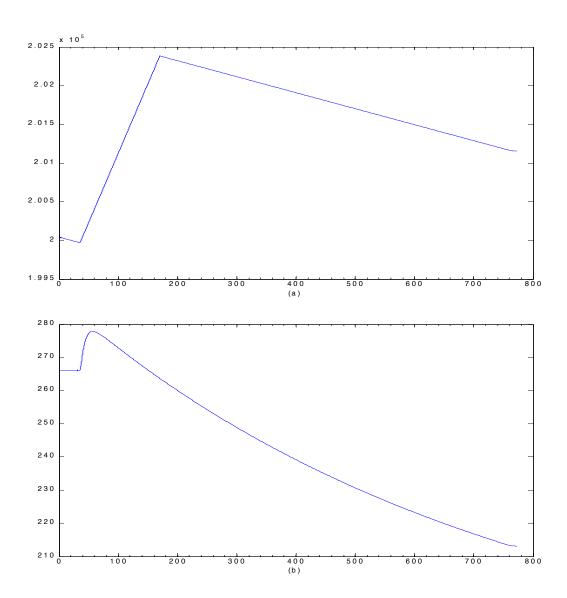

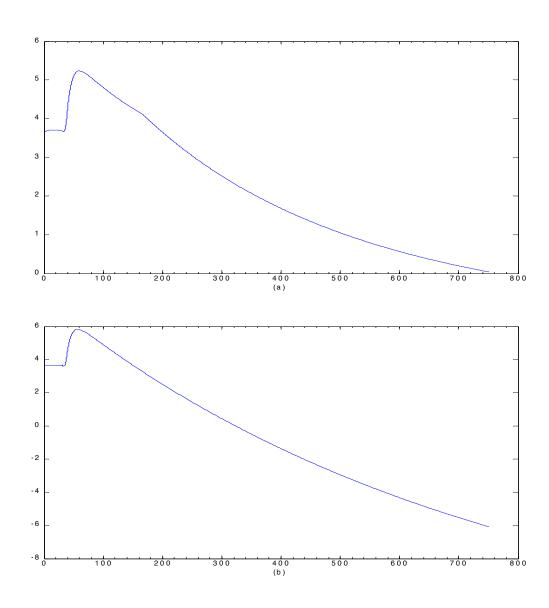

Device power transients have then been computed. Neutrons and prompt gamma contributions to sample heating are highlighted.

Significant difference in neutron and gamma contribution is due to higher MOLFI enrichment. Neutron contributions account for fission products initial kinetic energy and scattering reactions. Then a relatively higher fission rate changes fission-to-gamma balance in energy deposition.

#### 2.5 Conclusions and Perspectives

JHR future CEA material testing reactor is expected to perform several experiments on fuel samples inside reflector. Power transients are worth to be evaluated in these devices aiming at cooling system design and accident scenario simulations.

In the present analysis two shutdown transients have been considered – namely Normal Shutdown and Safety Shutdown. DULCINEE neutron kinetics code has been utilised for reactor core power evolution. On the other hand, reflector-core coupling has been computed by means of TRIPOLI 4.7 Monte Carlo transport code.

Then the most conservative control rod insertion configurations have been chosen and finally it has been possible to obtain the device power transients.

Energy deposition calculation through Monte Carlo method allowed computing different contribution in sample power regarding neutron-induced reactions and gamma heating.

Next task will be about the evaluation of a model which takes into account a multi-point kinetics approach in order to highlight core contribution to device heating. On the other hand an evaluation of the device multiplication contribution is envisaged.

Instead of weighting reaction rates necessary to compute kinetics constants, a twofold neutron transport approach is conceived: prompt and delayed neutrons are then considered with respect to their own time scale and multiplication reactions.

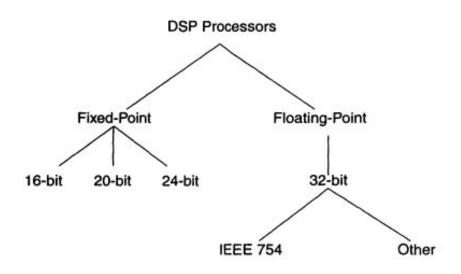

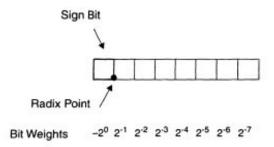

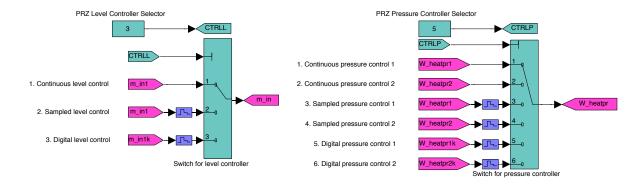

#### 3 References